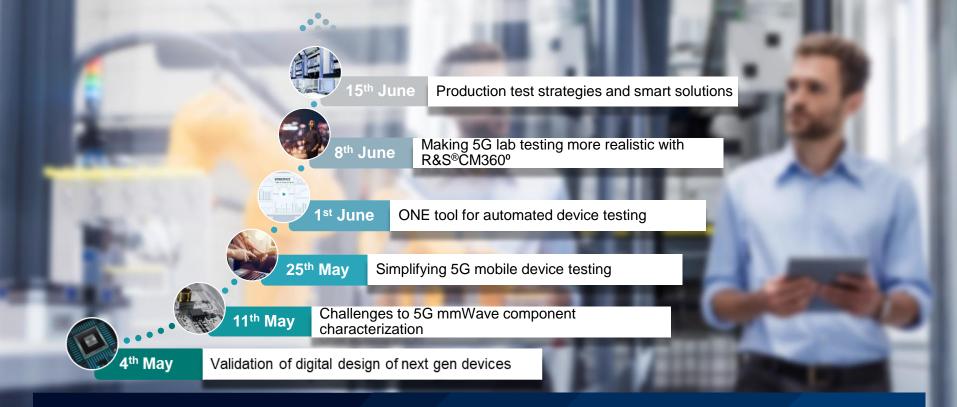

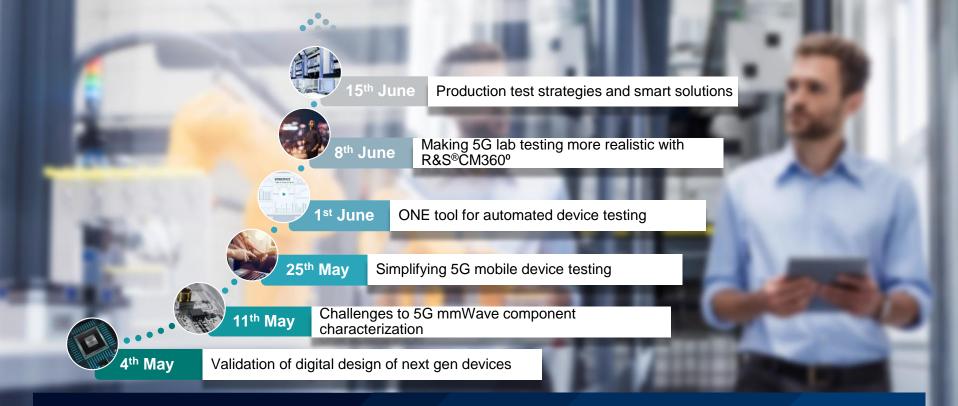

#### Webinar series: 5G Device Testing Journey VALIDATION OF DIGITAL DESIGN OF NEXT GEN DEVICES

CS Wong Oscilloscope Product Manager Asia

#### **ROHDE&SCHWARZ**

Make ideas real

#### **5G DEVICE TESTING JOURNEY**

Webinar Series

#### TOPICS

- ► What is in next gen?

- ► Base Station / Cellular Device Architecture

- ► High Speed Digital Interfaces

- Power Integrity

- ► Summary

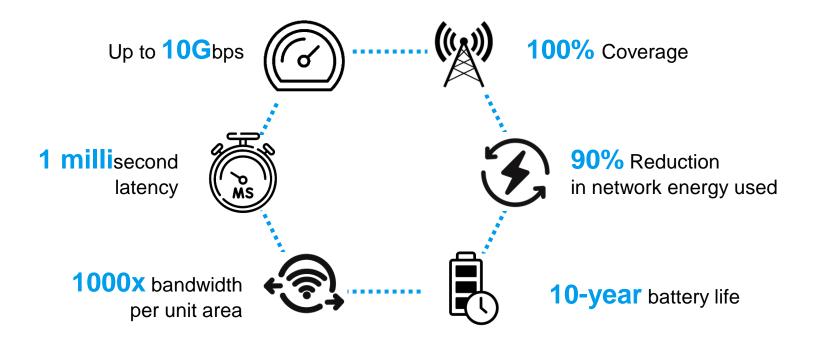

#### **KEY DRIVERS BEHIND THE NEXT GEN NETWORK & DEVICES**

### **DIGITAL LEAP IN NEXT GEN DEVICES**

# Warp-Speed processing

Rohde & Schwarz

Camera Resolution

#### Connectivity

#### **Battery Life**

Crystal Clear Display Refresh Rate

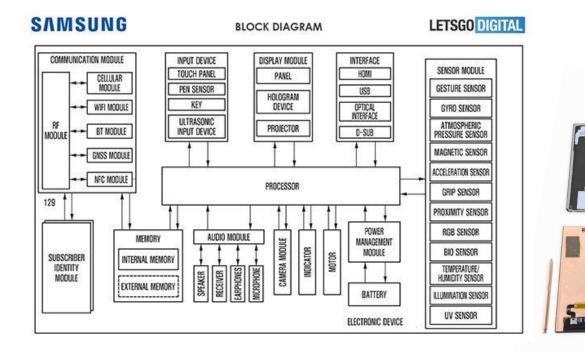

## **DEVICES ARE COMPLEX SYSTEM**

# **NEXT GEN DEVICES TRENDS**

**Digital Design & Power Trends**

- Memory: LPDDR4 -> LPDDR4x -> LPDDR5 starts

- Digital Processor: 7nm -> 5nm -> 3nm planned for 21/22

- ► Display interface: higher resolution

- ► Camera interface: higher resolution

- Additional sensors / health features

- ► Data / charging: USB -> USB Type C -> Wireless / Wireless Charging (Qi)

- Power management: plenty of PMICs

- ► Battery technologies: longer battery time

- ► Integration: Multi-chip, System-on-a-chip, etc.

#### **RF Trends**

- More Radios for new cellular and non-cellular standards

- MIMO antennas

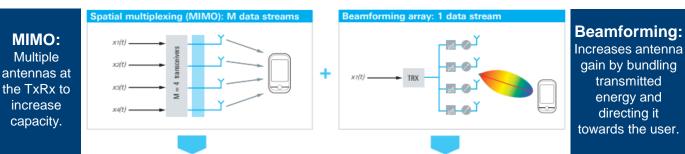

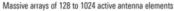

### **INCREASING MIMO DEGREES & BEAMFORMING**

- increase bandwidth (mmWave)

- massive MIMO

- beamforming

- virtualized network architecture

Massive MIMO: Very high number of antenna elements at the transceiver. Combination of beamforming and spatial multiplexing.

Increasing demand for higher MIMO degree.

Operators with mid-band spectrum show greater confidence in Massive MIMO, e.g. China, US. Beamforming as an essential measure to increase system efficiency, especially for mmWave.

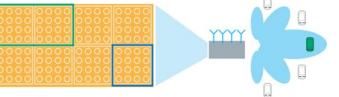

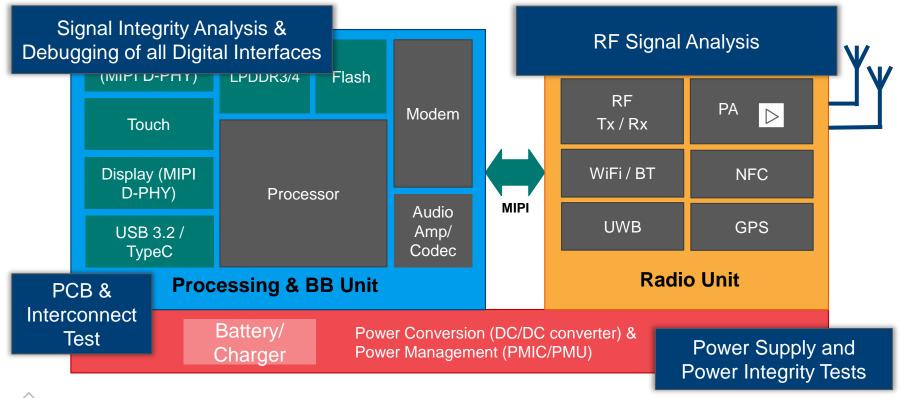

### **BASE STATION / CELLULAR DEVICE ARCHITECTURE**

Review of key components and how to address their testing.

#### **5G BASE STATION ARCHITECTURE** Digital Design, Power and RF Components

#### **5G CELLULAR DEVICES ARCHITECTURE** Digital Design, Power and RF Components

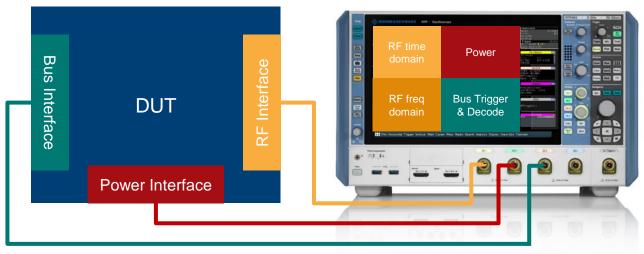

#### **SYSTEM-LEVEL DEBUGGING** MULTIDOMAIN ANALYSIS

CAN,UART ... MIPI-RFFE CIPR, Ethernet, PCIe, USB, MIPI-DPHY, (LP)DDR, etc. System-level Debugging

- Combine multiple measurements from different DUT interfaces on the same screen

- Look for possible correlations to determine causes of signal anomalies

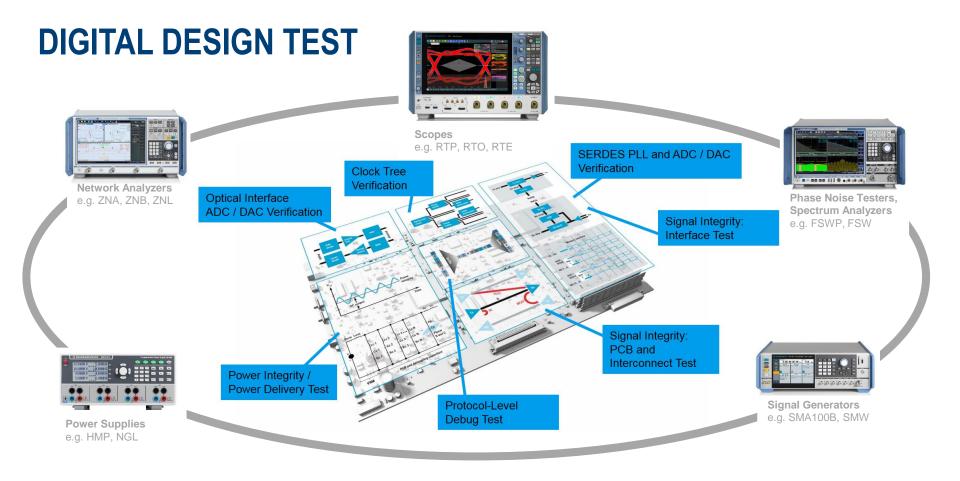

#### HIGH SPEED DIGITAL INTERFACES

Why fast and reliable signal integrity solutions including PCB and interconnect tests are so important for integration of High Speed Digital Interfaces?

#### HIGHSPEED DIGITAL INTERFACES CHALLENGES

- Signal integrity challenges due to increasing data rates

- Interference issues due to increasing level of integration

For optimal Signal Integrity analysis – T&M equipment needs to collect statistical data fast.

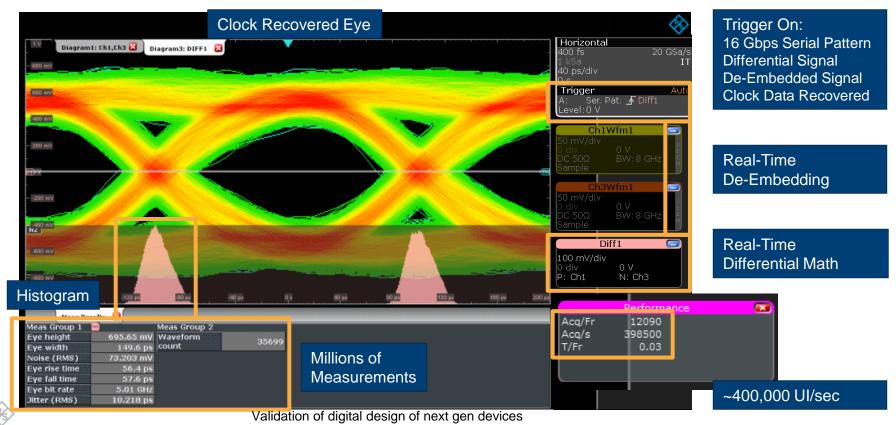

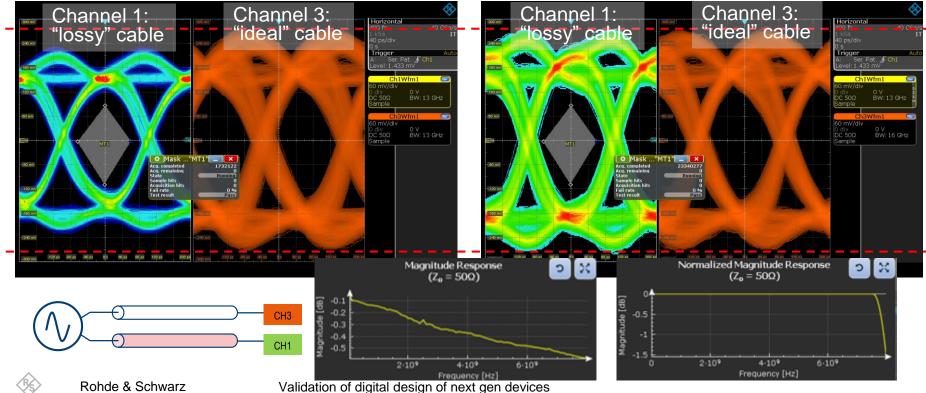

#### HIGH SPEED DIGITAL INTERFACES Require Dedicated Tests for Verification & Debugging

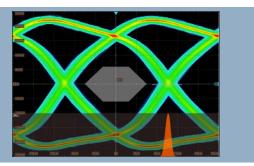

#### Eye Diagram

- Fast update rate for statistical confidence

- Continuously operating Clock-Data-Recovery (CDR)

- Mask tests

- Deembedding function to compensate transmission loss

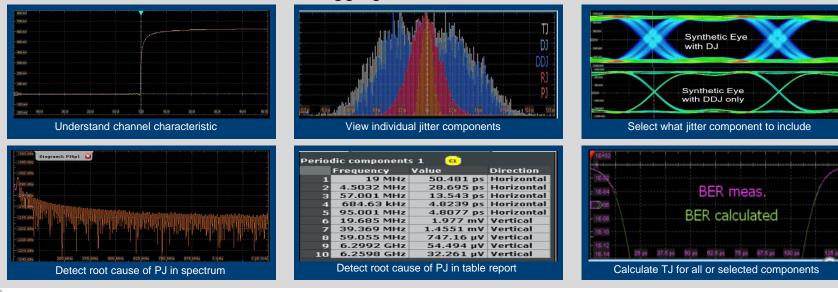

#### **Jitter Analysis**

Break-down of jitter and noise into individual components for characterization & debugging

#

#### Automated Compliance Tests

Verify compliance of the physical layer to interface standards and report results

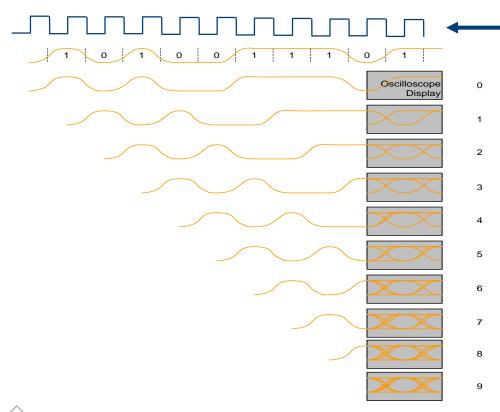

#### **EYE DIAGRAM BASICS**

### **GENERATING EYE DIAGRAMS**

Reference clock Triggers oscilloscope

> Waveform is sampled synchronous with the bit rate of the signal and randomly over time

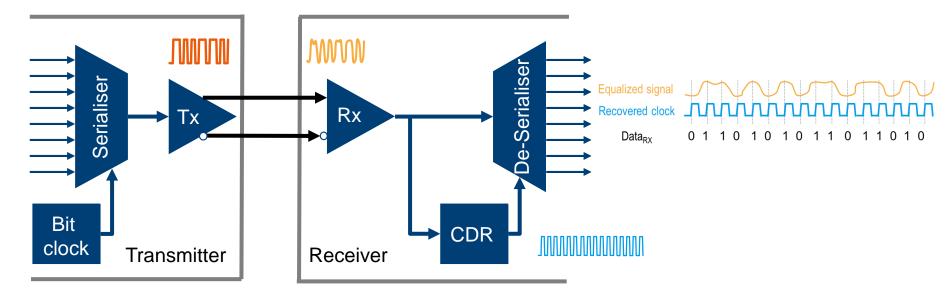

#### **REFERENCE CLOCK FOR EYE DIAGRAMS** CLOCK-DATA-RECOVERY

- Timing Reference can be from a reference clock (parallel clock signal) or from the data signal itself (embedded clock signal)

- Clock data recovery is typically uses a Phase Locked Loop (PLL) or Delay Looked Loop (DLL)

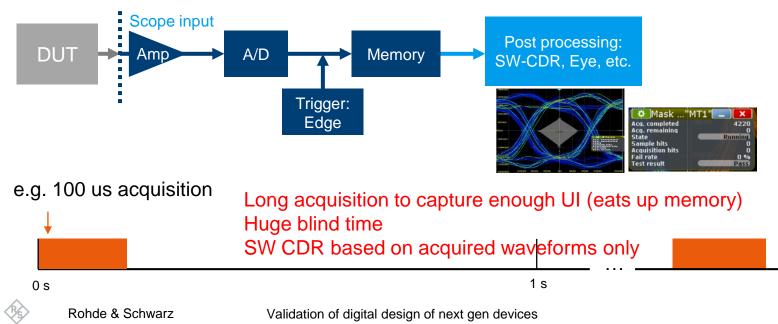

## **EYE DIAGRAM IN POST-PROCESSING**

- ► Analysis based on a single acquisition with long Record length and SW-CDR in postprocessing

- Acquired waveform is "folded" over into an eye based on software recovered clock

- CDR settling time (typ. >10us) and new synchronization for every new acquisition

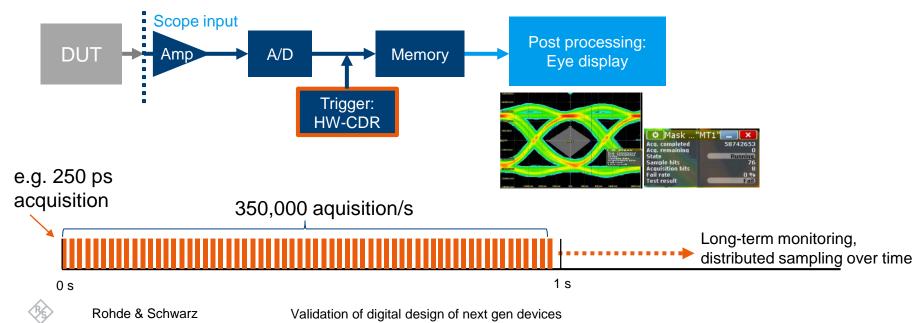

### **REALTIME EYE DIAGRAM**

- ► Analysis based on a multiple acquisition, short Record Length and CDR in Hardware

- Acquired bits are overlaid to an eye based on HW-CDR timing

- CDR looked once and runs continuously

### **MAKING IT FAST – REAL-TIME ANALYSIS**

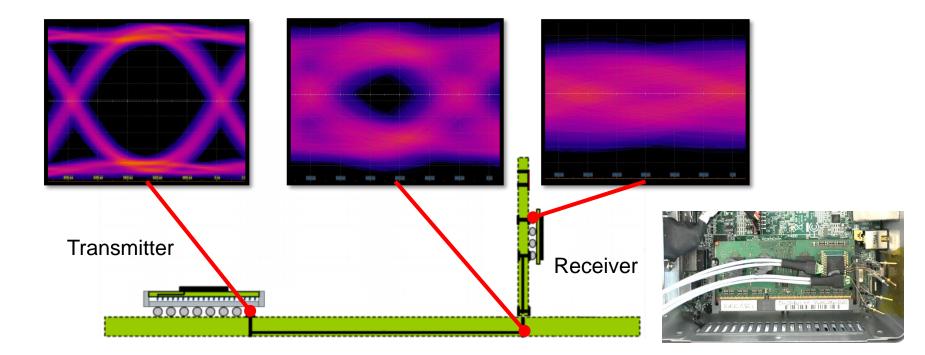

### **CONCEPT OF DEEMBEDDING**

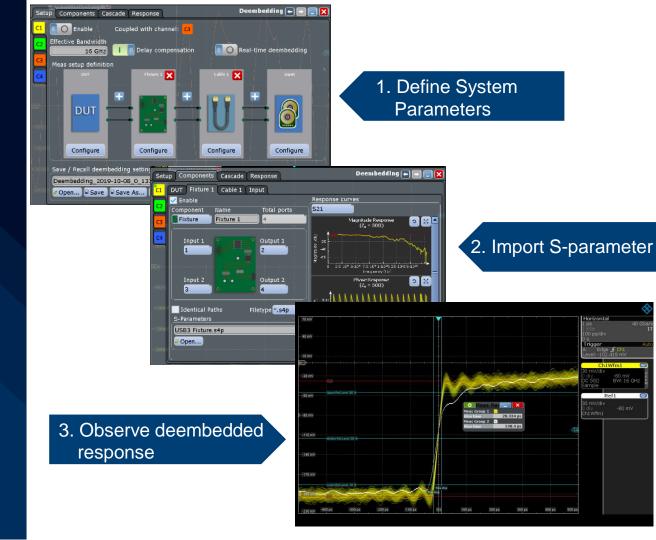

#### DEEMBEDDING MADE EASIER

- Option RTO/P-K121 + RTP-K122

- SW and HW (Realtime)

- Applied during acquisition

- Trigger on de-embedded signal

- No update rate change

- Proven Cable / Probe

- removes transmission loss effects

- B7 pulse source

#### **EXAMPLE – USB 3.2 GEN1 SIGNAL**

#### De-embedding: OFF

#### De-embedding: ON

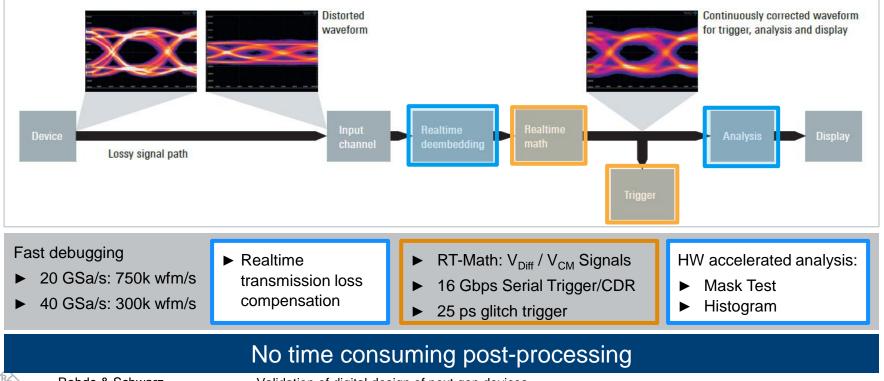

### **REALTIME SIGNAL INTEGRITY UP TO 16 GHZ**

#### Realtime Deembedding Architecture

Rohde & Schwarz

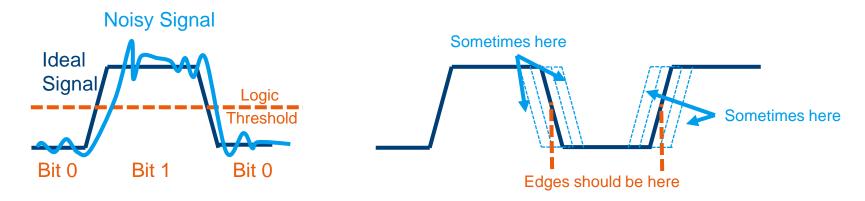

### WHAT IS JITTER?

**Timing Uncertainty**

Frequency Domain Phase Noise Time Domain Jitter

Jitter is the short-term variations of a digital signal's transition edges from their ideal position

### **REASONS TO MEASURE JITTER**

#### Standards Requirement

| Table 4-4: Total System Jitter Budget for 5.0 GT/s Signaling |                 |             |                                  |  |

|--------------------------------------------------------------|-----------------|-------------|----------------------------------|--|

| Jitter Contribution                                          | Max RMS Rj (ps) | Max Dj (ps) | Tj at BER 10 <sup>-12</sup> (ps) |  |

| Тх                                                           | 1.4             | 30          | 50                               |  |

| Ref Clock                                                    | 3.1             | 0           | 43.6                             |  |

| Media                                                        | 0               | 58          | 58                               |  |

| Rx                                                           | 1.4             | 60          | 80                               |  |

| Linear Total Tj:                                             |                 |             | 231.6                            |  |

| Root Sum Square (RSS) Total Tj:                              |                 |             | 200                              |  |

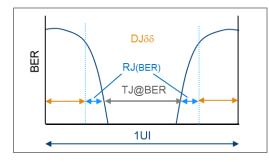

Bathtub Plot

Measure Bit Error Ratio (BER) to 10<sup>-12</sup>

"1 Bit Per every 1 Trillion Bits"

Oscilloscopes estimates it

USB spec require RJ, DJ and TJ @ 10<sup>-12</sup>

Standards require separation and provide limits

Find root cause sources

What-if you fix it? Analysis

### **JITTER COMPONENTS**

Total Jitter is composed out of several jitter contributions:

- Random Jitter: "unbounded"

- Deterministic Jitter: usually "bounded"

### **EVOLUTION OF SEPARATION ALGORITHMS**

| Jitter Separation<br>"Tail"-fitting &<br>Dual-Dirac-Model | Extension with<br>Transformation into Q-<br>Space | R&S's modern approad<br>Signal-Model-based |    |

|-----------------------------------------------------------|---------------------------------------------------|--------------------------------------------|----|

| 2000                                                      | 2008                                              | 202                                        | 20 |

| Extensions DDJ/ISI/DDC and<br>spectrum view for PJ, etc.  |                                                   | Extension with<br>Noise Separation         |    |

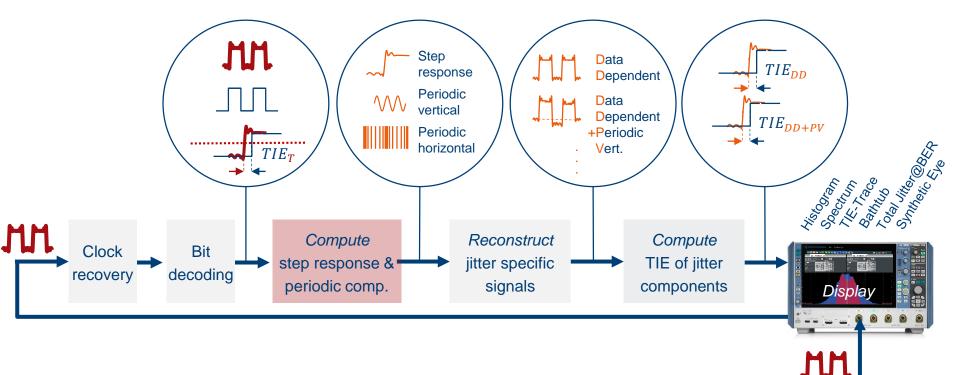

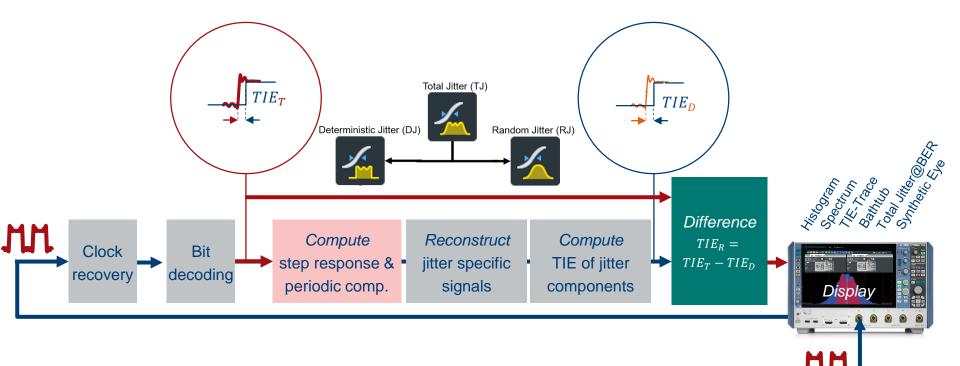

#### **NOVELL R&S APPROACH DETERMINISTIC COMPONENT**

#### **NOVELL R&S APPROACH RANDOM COMPONENT**

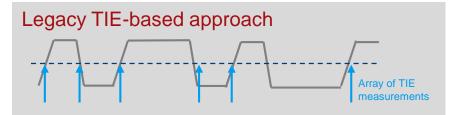

Use more result data for faster debugging

Reduce Signal information to a set of TIE measurements at a voltage threshold

#### R&S's Signal Model-based approach

Calculated step response that describes deterministic behavior of the transmission system

Parametric signal model with all signal information for most accurate and reliable jitter decomposition

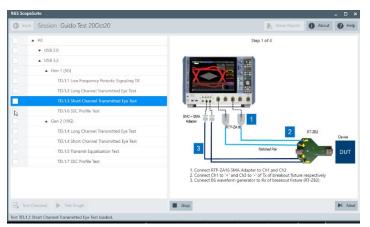

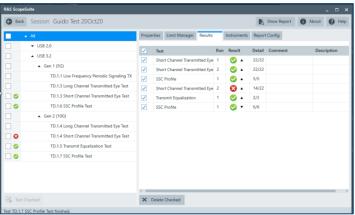

#### AUTOMATED COMPLIANCE SOFTWARE

### **TESTING BASED ON COMPLIANCE REQUIREMENT**

Electrical specifications in each standard committees covers all the measurement requirement but it will be difficult to manually execute all the requirements

- Specified measurement algorithm and setup

- Additional signal processing as per required by standards (deembedding & CDR)

- Guidance to depict the set necessary test modes and fixtures setup

Most standard bodies still required DUT to be tested by official test house or allow submission of compliance report.

# **SCOPESUITE COMPLIANCE**

- Automated Compliance Test following standards

- ► R&S ScopesSuite Wizard

- Guided test execution

- Flexible test operation (incl. re-tests)

- Limit manager

- Detailed test reports

Validation of digital design of next gen devices

### **POWER INTEGRITY**

What are the right tools and analyzing functions for appropriate characterizing & debugging?

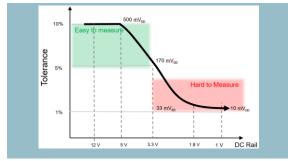

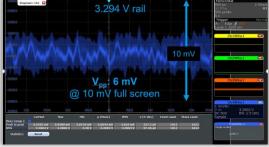

## POWER INTEGRITY CHALLENGES

- Increasing number of power rails

- Lower margins due to lower supply voltages

- Interferences due to dense designs of mixed technologies

An optimal solution for characterizing and debugging DC power rails demands suitable probes & oscilloscopes.

## **POWER INTEGRITY** Requires Dedicated Tools for Verification & Debugging

### The Right Scope

- ► Fast update rate

- Min. vertical scale: 1..2 mV/div in HW at full bandwidth

- ► Low noise

- Support of specialized probes also on high-performance class instruments

#### **Specialized Probes**

- ► Power Integrity Probe

- Bandwidth >2 GHz

- Low noise with 1:1 attenuation

- Extended offset range

- Connectivity

- ► Current probes, etc.

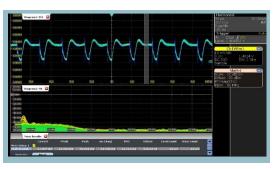

#### Dedicated Analysis Functions

#### Typical measurements

- ► Ripple, Load step response

- ► Power-up/down, Sequencing

- Drift over temperature and input voltage

- ► EMI debugging / harmonic analysis

### R&S POWER INTEGRITY SOLUTION

- ► Low Noise

- Fast FFT

- Fast Update Rate

- Low-Price Alternatives

-RTM / RTA Oscilloscopes

- Superior Power Rail Probes

Providing Unique Power Integrity Analysis Functions

## **DEDICATED POWER RAIL PROBING SOLUTION**

#### RT-ZPR20/40 Power Rail Probes

- ► Active, single-ended probe

- ► Very low noise with 1:1 attenuation

- ► Best in class offset compensation capability

#### RT-ZVC Probe for Power Consumption

- ► 18-bit vertical resolutions for each channels

- ► 0.1% measurement accuracy

- <2 nA AC RMS noise</p>

Validation of digital design of next gen devices

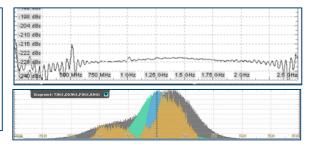

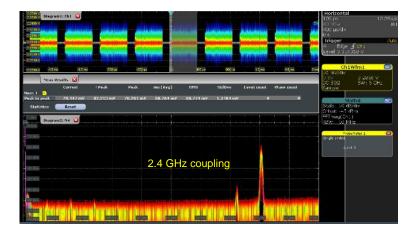

# **UNIQUE ANALYSIS FUNCTIONS IN ONE INSTRUMENT**

#### Superior FFT Performance

- ► Fast and responsive FFT to detect interferer

- ► Multi-channel Math FFT for comparison

- ► Time and frequency domain correlation

#### EMI Debugging Capability

- ► Log scale display to match Test Receiver presentation

- ► Limit line capability with zone trigger to detect violation

- Math on FFT for further EMI testing & analysis

## **DEDICATED INSTRUMENT FOR SPECIALIZED TESTING**

Using the best tool for specific measurements.

### R&S RTP HIGH-PERFORMANCE OSCILLOSCOPE

- 4-16 GHz bandwidth

- Dedicated hardware for real-time Signal-Integrity

- Most compact & silent for everyday use in the lab

**Providing Unique Signal Integrity Analysis Functions**

## **SUMMARY**

- Digital design is the backbone for the next generation devices and infrastructures

- ► Technology advances push complexities into design as well as measurement requirements

- Signal integrity ensure best performance for design interconnects which need a versatile tool to help characterizing and debugging

- Power integrity is often forgotten but plays an important role that affects the design performance

Next generation build on the fundamental performance of the devices and infrastructure, making sure these designs works will be crucial for your 5G Testing Journey!

## **5G DEVICE TESTING JOURNEY**

Webinar Series

5G Device testing journey

MAY THE FORCE BE WITH YOU

For more information: www.rohde-schwarz.com

### **ROHDE&SCHWARZ**

Make ideas real