## 從設計到實現RF待測物 — EDA模擬中RF功率放大器線性化的優勢

Dr. Milton Lien, Sr. Principal Application Engineer, Cadence Arsene Chen, Application Engineering Manager, R&S Taiwan

#### **ROHDE&SCHWARZ**

Make ideas real

#### **AGENDA**

- ► Introduction

- New joint solution from R&S and Cadence

- ► Introduction to the Cadence AWR Design Environment<sup>®</sup> platform

- ► Live demonstration of joint solution I

- Combination of Cadence VSS EDA with Direct DPD by Rohde & Schwarz

- ► Live demonstration of joint solution II

- ► Summary

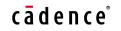

### WHY COLLABORATION?

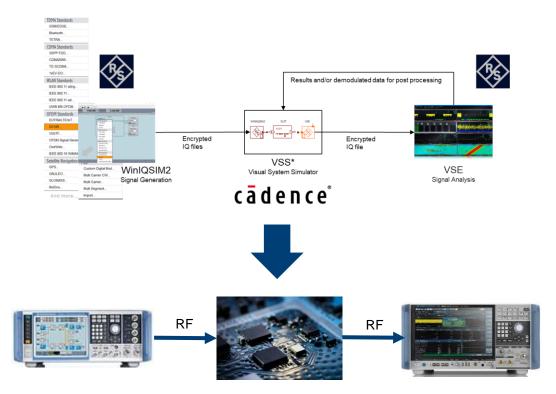

Connecting EDA simulation and hardware test

cādence°

Connecting EDA simulation and hardware test

cādence°

Connecting EDA simulation and hardware test

cādence°

Connecting EDA simulation and hardware test

cādence°

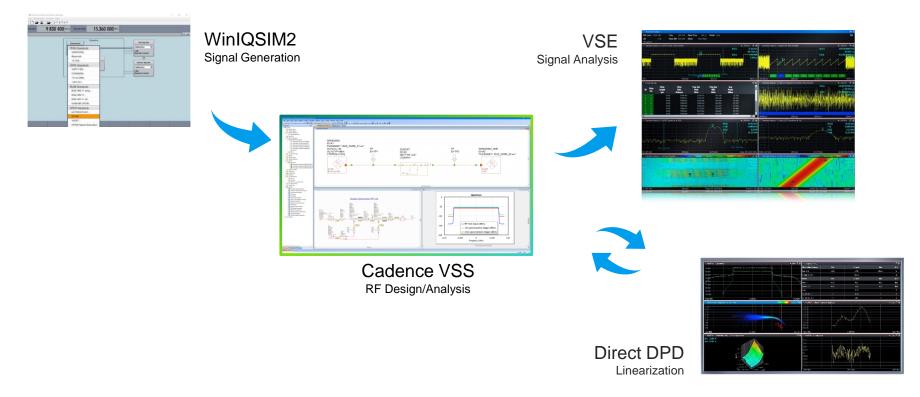

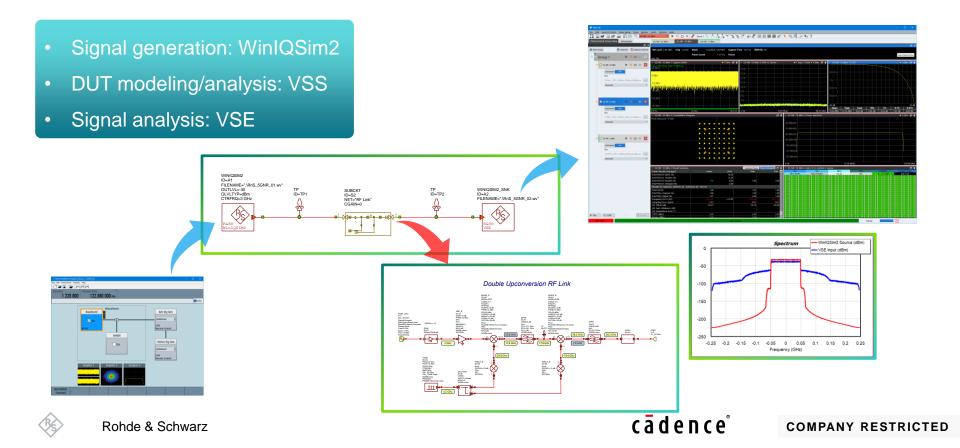

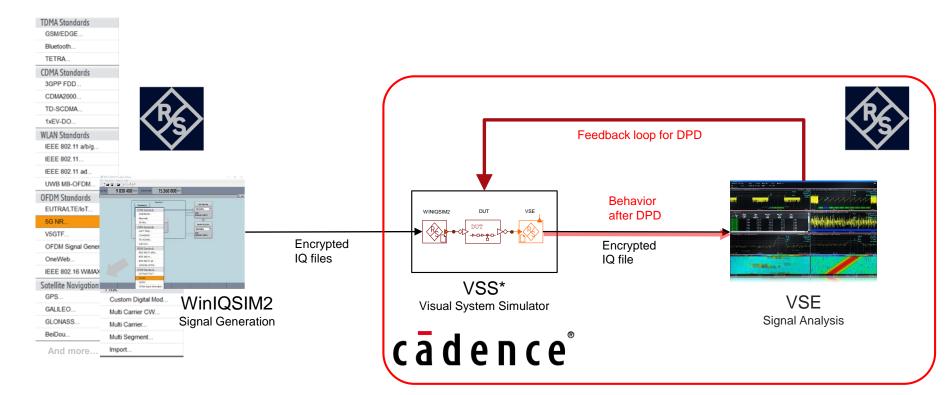

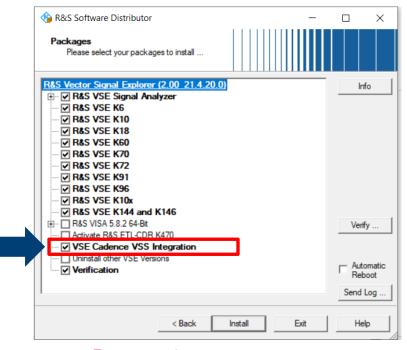

#### New software product: R&S VSESIM-VSS

- VSE included

- Plug-in for VSE and WinIQSIM2 included in VSE installer

- WinIQSIM2 license included separate installer

Focus on components like power amplifier all the way to complex RF systems as in base station radios, radar systems or satellite links

#### ► Goal: Enabling first pass design

- Complex new communication systems support high bandwidth and complex scenarios

- Interaction between components in RF system amplified with modern wideband systems

- Use of real signals in EDA system simulation to verify resulting FOM of EVM

- Maximize correlation with same signal in simulation and physical test

- Investigate linearization (DPD) already in simulation

- Streamlined process from design to implementation

Connecting EDA simulation and hardware test

# COOPERATION: 🐼 AND cādence<sup>°</sup> GETS YOU FURTHER

- ► What to do when having half the system ready?

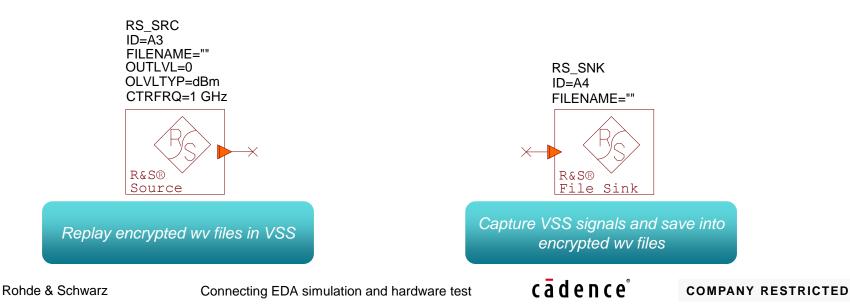

- VSE sink can be placed anywhere in the VSS chain and get the IQ data to plug into SMW ARB

- HIL scenarios

VSS\* Visual System Simulator

Connecting EDA simulation and hardware test

cādence<sup>°</sup>

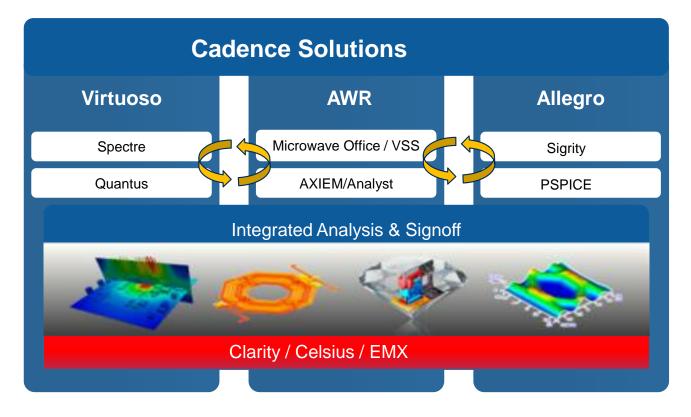

### CADENCE INTRODUCTION

Introduction to Cadence world and family of solutions

► Live demo

# Ask Cadence 提問禮 ¥

cādence

留言提問**Cadence**,即有機 會獲得限量好禮 「療癒拍拍海豹燈」!

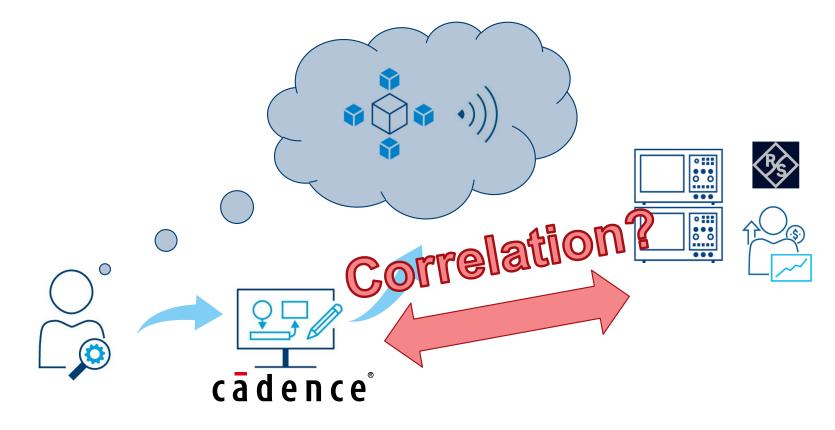

#### **ROHDE SCHWARZ – CADENCE COLLABORATION**

WinIQSim2 – VSS – VSE Product integration

Dr. Milton Lien, Sr. Principal Application Engineer, Cadence

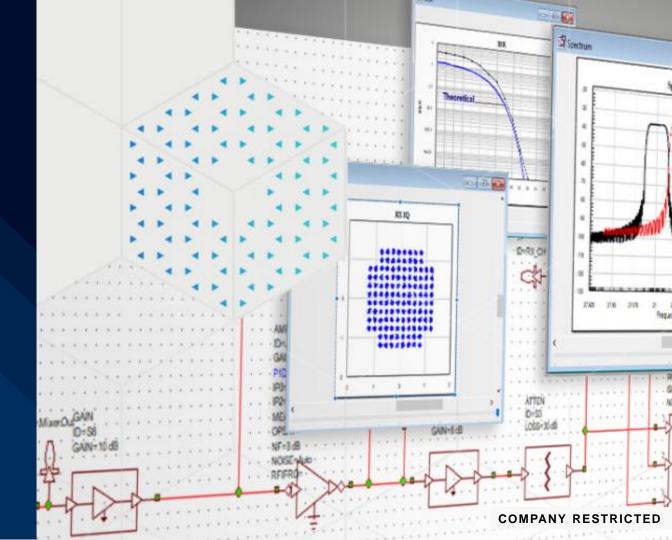

#### **AWR RF WITHIN CADENCE**

COMPANY RESTRICTED

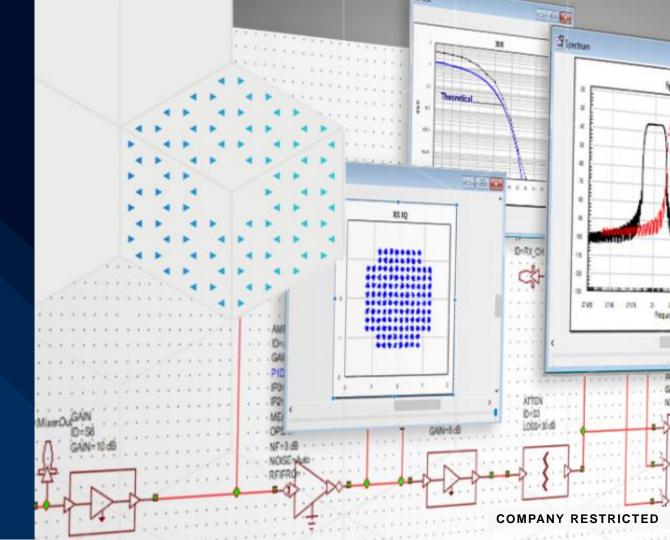

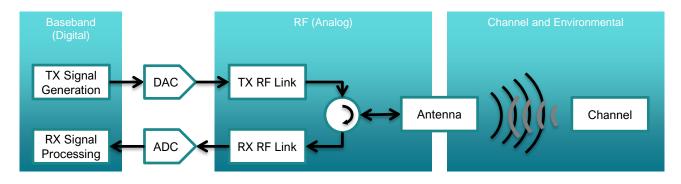

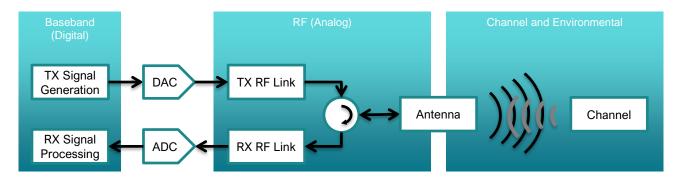

#### VISUAL SYSTEM SIMULATOR ™ (VSS)

- Part of the Cadence AWR Design Environment<sup>®</sup> platform

- Design and analyze anything from simple RF links to complete comm systems

- RF budget analysis, RF spur heritage

- Modeling and time-domain simulation of complete communication links

- Phased array design, standard communication libraries, etc.

VSS includes models for every component in such systems!

COMPANY RESTRICTED

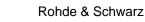

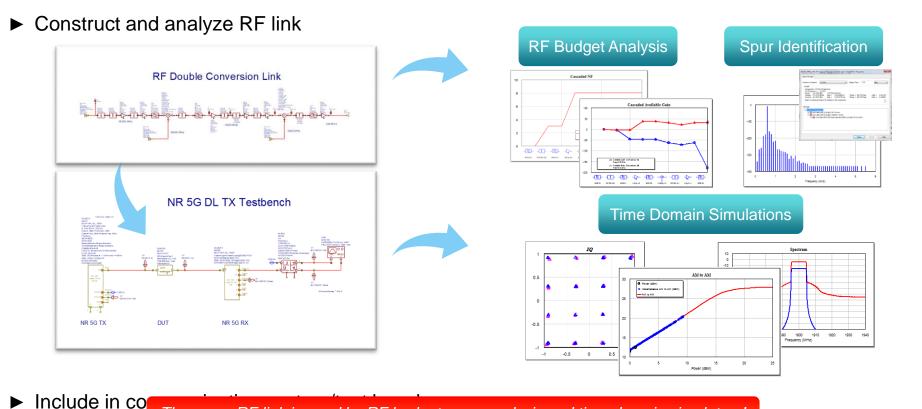

#### **RF SYSTEM DESIGN AND ANALYSIS FLOW**

Include in communication system/test bench

The same RF link is used by RF budget, spur analysis and time domain simulators!

COMPANY RESTRICTED

#### **VSS CUSTOMER BASE**

- ► RF Component and Circuit Designers

- RF System/Sub-System Designers

- Baseband System Designers

Design often leads to prototyping and measurements in lab

Need for instrumentation and fully spec-compliant signals!

Rohde & Schwarz

cādence° c

### **R&S – CADENCE INTEGRATED DESIGN FLOW**

#### **DEMO OF WINIQSIM2 – VSS – VSE CO-SIMULATION**

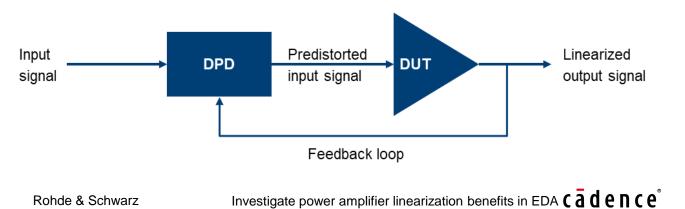

#### LINEARIZATION FOR RF POWER AMPLIFIER

Investigate power amplifier linearization benefits in EDA C a d en c e

Investigate power amplifier linearization benefits in EDA Cade a Ce

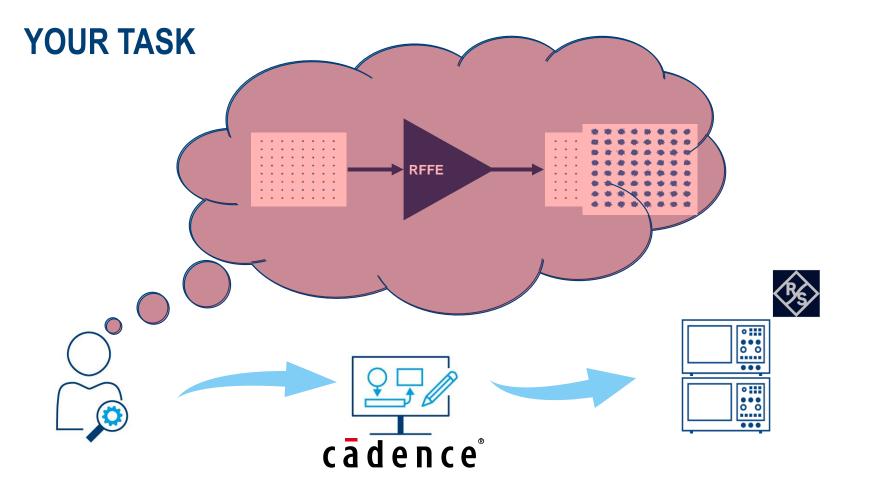

### WHY LINEARIZATION?

- Challenging RF signals on RF frontends

- 5G in mmWave and RF, mMIMO, beamforming, increasing bandwidth, higher order modulations, digital payloads, wideband Electronic Warfare (EW)

- Significant power consumption is in the RF Front-End (RFFE)

- Operating close to saturation offers best energy efficiency

- Technologies such as GaN absolutely require digital predistortion for linear operation

- Various PA topologies studied

- Doherty, Load Modulated Balanced Amplifier (LMBA), Outphasing, ...

- ▶ PA gains in efficiency but is highly non-linear

→ Linearization is a \_MUST\_

Investigate power amplifier linearization benefits in EDA C a d e n c e

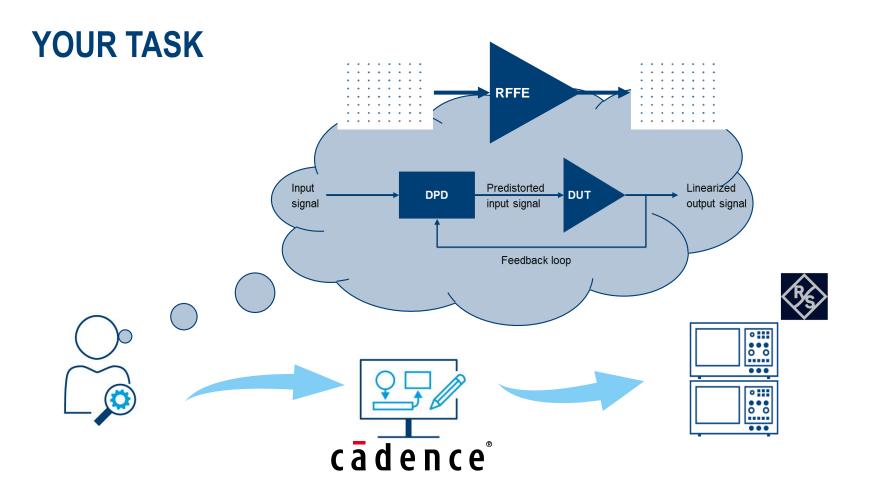

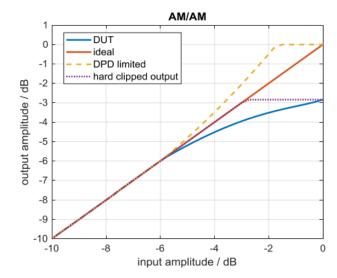

### LINEARIZATION / DPD

- PAs often driven close to saturation for max power efficiency, but in non-linear operation: compression & memory effect

- ► Linearization for compensation

- Understand system level performance with ideal predistortion needed

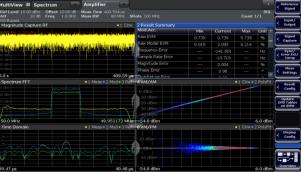

Figure 4 Overview plot: measured AM/AM, ideal output, predistorted input signal, and target output signal (hard clipped)

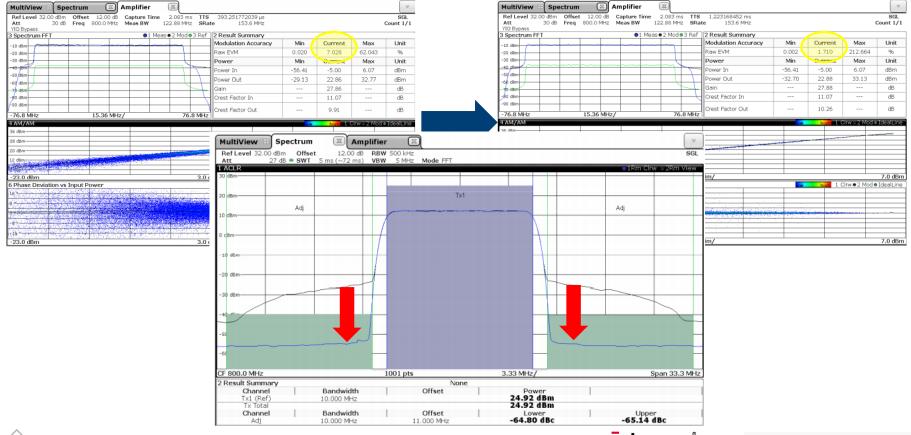

### **DIGITAL PREDISTORTION: BEFORE AND AFTER**

Investigate power amplifier linearization benefits in EDA Cade Cade Ca

Investigate power amplifier linearization benefits in EDA C a d e n c e

### **VSS BRIEF INTRODUCTION**

**RF** System Design and Analysis

Dr. Milton Lien, Sr. Principal Application Engineer, Cadence

#### VISUAL SYSTEM SIMULATOR ™ (VSS)

- Part of the Cadence AWR Design Environment<sup>®</sup> platform

- Design and analyze anything from simple RF links to complete comm systems

- RF budget analysis, RF spur heritage

- Modeling and time-domain simulation of complete communication links

- Phased array design, standard communication libraries, etc.

VSS includes models for every component in such systems!

COMPANY RESTRICTED

#### **RF SYSTEM DESIGN AND ANALYSIS FLOW IN VSS**

The same RF link is used by RF budget, spur analysis and time domain simulators!

**COMPANY RESTRICTED**

Rohde & Schwarz

Investigate power amplifier linearization benefits in EDA Cade Cade Ca

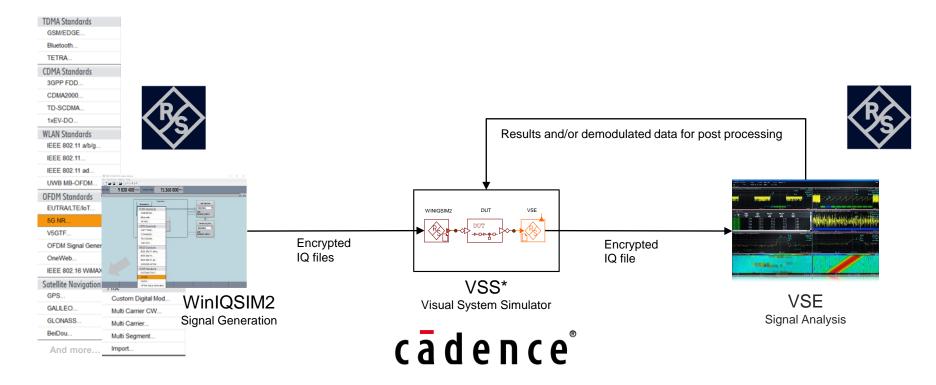

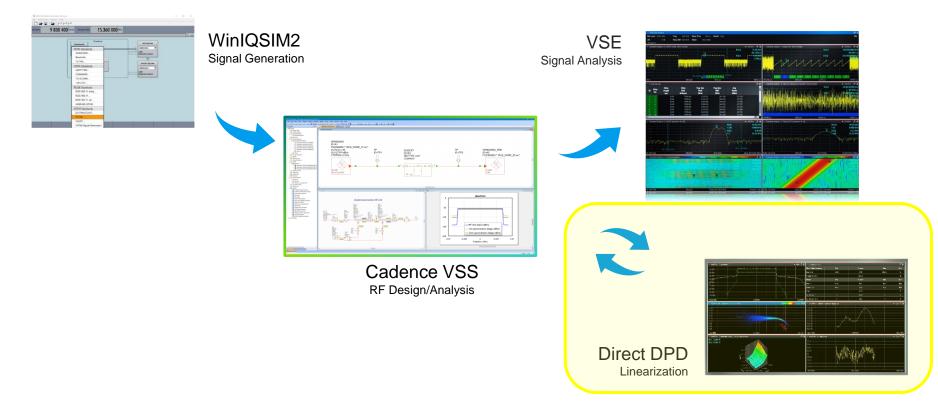

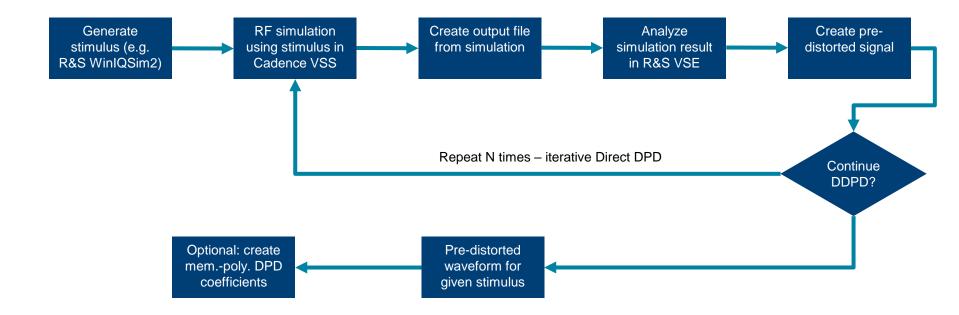

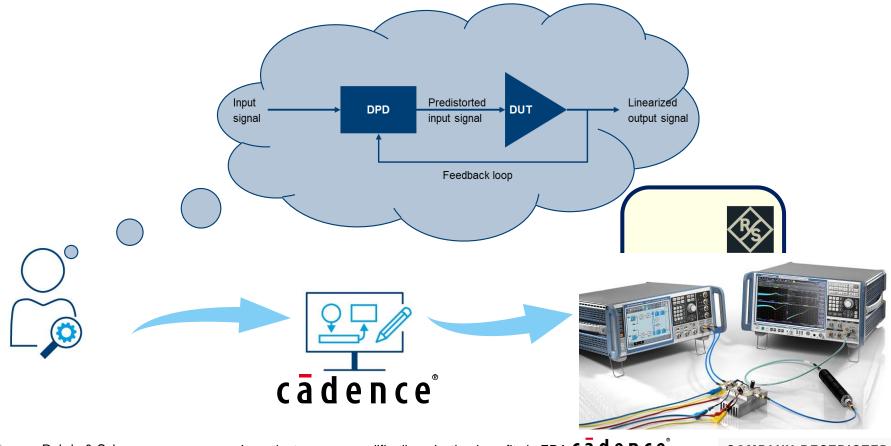

### **PRE-DISTORTING AN RF-AMPLIFIER PURELY IN SIMULATION**

Script controlling both

software packages:

Cadence VSS and R&S VSE

#### RF simulation of PA in Cadence VSS

Iterative Direct DPD in R&S VSE

| DPD Demo        |                                       |                                       |                                       |                                               |

|-----------------|---------------------------------------|---------------------------------------|---------------------------------------|-----------------------------------------------|

|                 |                                       |                                       |                                       |                                               |

|                 |                                       |                                       |                                       |                                               |

|                 |                                       |                                       |                                       |                                               |

|                 |                                       |                                       |                                       |                                               |

|                 |                                       |                                       |                                       |                                               |

|                 |                                       |                                       |                                       |                                               |

|                 |                                       |                                       |                                       |                                               |

|                 |                                       |                                       |                                       | RS_SNK · · · · · · · · · · · · · · · · · · ·  |

| <u></u>         | <u></u>                               |                                       |                                       | ID=A3 · · · · · · · · · · · · · · · · · · ·   |

| RS_SRC          | · · · · · · · · · · · · · · · · · · · |                                       |                                       | FILENAME="\waveforms\sim_out:wv"              |

| 1D=A2 · · · ·   | <mark>.</mark>                        |                                       |                                       | START=0 · · · · · · · · · · · · · · · · · · · |

| FILENAME="/./wa | veforms\sim_in.wv" · · · ·            |                                       |                                       | DUR=1.6e-3                                    |

| OUTLVL=-7.55387 | /153683 · · · · TP · · ·              | AMP TONN                              |                                       | TIMETY/P=Time                                 |

| OLVLTYP=dBm     | · · · · · · ID=RefS                   | gnal                                  |                                       | STOPSIM=Yes                                   |

| CTRFRQ=1.85 GH  | <u>dz</u> a <u></u>                   | FILEs" \testdata\skvfl                | 6391-12 ann"                          | SIGDLY=Ignore                                 |

|                 |                                       |                                       | · · · · · · · · · · · · · · · · · · · |                                               |

| 62 1            |                                       |                                       |                                       | 62                                            |

|                 |                                       |                                       |                                       |                                               |

| - I - X¥ 🕈      | - <b>I</b> •                          |                                       |                                       | P = 2 √ √ 2 / 1 = 2 = 2 = 2 = 2 = 2 = 2       |

| R630<br>Source  |                                       |                                       |                                       | ReSe Sink                                     |

| Source          |                                       | · · · · · · · · · · · · · · · · · · · |                                       | Sink                                          |

| •               |                                       |                                       |                                       |                                               |

|                 |                                       |                                       |                                       |                                               |

|                 |                                       |                                       |                                       |                                               |

|                 |                                       |                                       |                                       |                                               |

|                 |                                       |                                       |                                       |                                               |

|                 |                                       |                                       |                                       |                                               |

|                 |                                       |                                       |                                       |                                               |

|                 |                                       |                                       |                                       | >                                             |

Investigate power amplifier linearization benefits in EDA Caden Ce

#### SCHEMATIC FOR PRE-DISTORTION IN RF SIMULATION CADENCE VSS – R&S VSE

Investigate power amplifier linearization benefits in EDA C a d e n c e

### DPD IN RF SIMULATION

- Live demo of the joint solution

- Linearization in Cadence VSS using R&S VSE toolset

#### YOUR TASK

Investigate power amplifier linearization benefits in EDA C a d e n c e

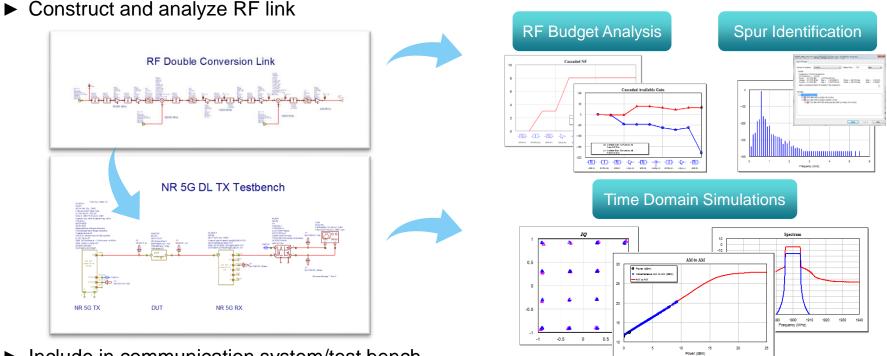

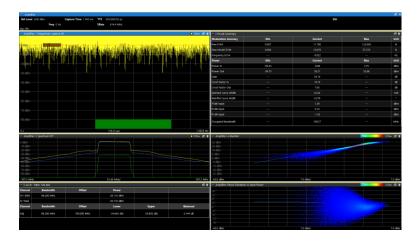

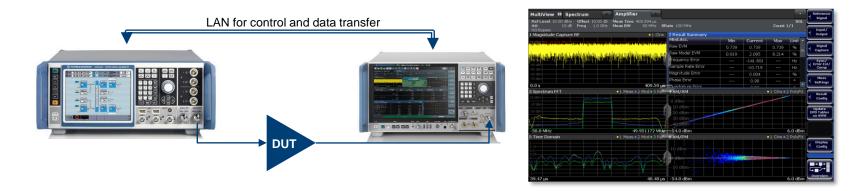

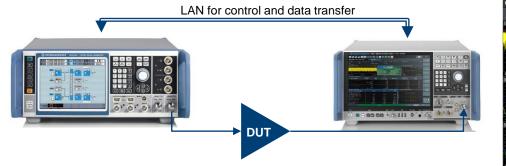

### **COLLECTING DATA ON A REAL POWER AMPLIFIER**

#### R&S®FSW-K18D Direct DPD

- Iterative approach

- Compensates for memory effects

- Excellent performance especially for amplifiers with memory effects

- Reference for best possible

- Suppliers typically do not have access to DPD algorithms used by system integrators

Investigate power amplifier linearization benefits in EDA C a d e n c e

### **CREATING THE MEMORY POLYNOMIAL DPD IN FSW**

#### R&S®FSW-K18D Direct DPD

- Iterative approach

- Compensates for memory effects

- Excellent performance especially for amplifiers with memory effects

- Reference for best possible

- Suppliers typically do not have access to DPD algorithms used by system integrators

#### R&S®FSW-K18M memory polynomial

- Memory polynomial model based on Direct DPD result

- Modeling can be adopted in order and memory depth

- Model verification on DUT

- Proves easy linearization of RFFE solution

Rohde & Schwarz

Investigate power amplifier linearization benefits in EDA Cade Cade Ca

#### COMPARISON SIMULATION VS. MEASUREMENT

Measurement and pre-distortion all PC-based (RF simulation + signal analysis)

## Measurement and pre-distortion on physical device

#### **SUMMARY AND CALL FOR ACTION**

onnecting EDA simulation and hardware test

### **HOW TO GET IT**

- ► R&S VSESIM-VSS, sold by R&S

- Latest version V17 of Cadence AWR VSS, sold by Cadence

- New R&S software product

- 12 month license

- All future updates, extensions and standards included

- 1 license VSESIM-VSS enables <u>all</u> WinIQSIM2 and VSE standards and features

- USB dongle or new software license for license server (in line with Cadence approach)

cādence°

#### SUMMARY

- First pass design through real target application signals

- Direct DPD to verify linearization possibilities already in simulation

- Streamlined process from design to implementation

- Correlation is given from simulation to real world test by applying same signals and demodulation

- Hardware in the loop to verify subset implementation complemented by simulation for system level verification

- Link to further Cadence tools through VSS

Connecting EDA simulation and hardware test

Find out more

#### www.rohde-schwarz.com

# Thank you!

#### **ROHDE&SCHWARZ**

Make ideas real