R&S RTP Oscilloscope

# (LP)DDR5 MEMORY INTERFACE SIGNAL INTEGRITY DEBUGGING & COMPLIANCE TESTING

Guido Schulze, Product Manager Oscilloscopes

Johannes Ganzert, Senior Application Engineer Oscilloscopes

#### ROHDE&SCHWARZ

Make ideas real

#### OUTLINE

- **DDR Memory Refresher**

- ► (LP)DDR5 Details

- ► Signal Integrity Debugging

- ► Compliance Testing with R&S ScopeSuite

- ▶ Live Demonstration

- ► Summary

#### DDR SDRAM

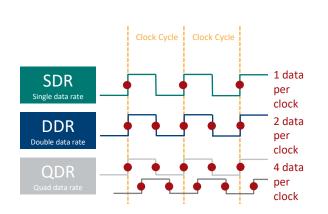

#### What is DDR?

- ▶ Double-Data Rate

- ▶ Data bit is transmitted at both rising and falling edges of clock

#### What is SDRAM?

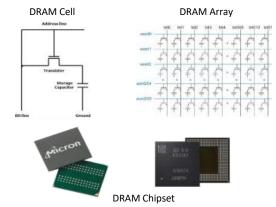

- ► Synchronous Dynamic Random Access Memory

- ➤ Volatile memory that can store data fast but temporarily

#### What is DIMM?

- ► Dual Inline Memory Module

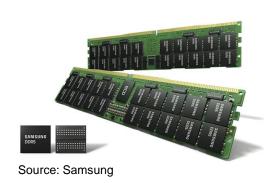

- ► Commonly found in PC & servers as array of SDRAMs

Unbuffered DIMM

Low Profile Unbuffered DIMM

Small Outline

DIMM

Micro-DIMM

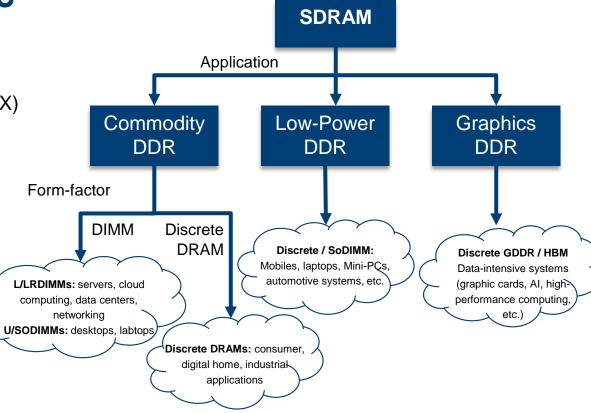

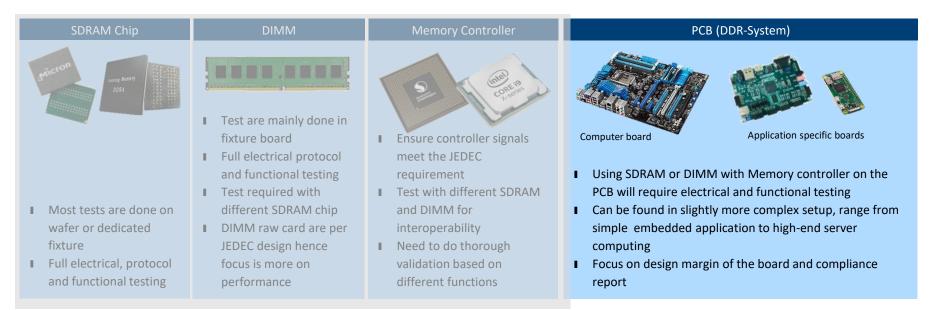

### **SDRAM APPLICATIONS**

#### ► SDRAM Types:

Main memory: DDRx(L)

Low Power / Mobile: LPDDRx(X)

Graphics: GDDRx(X)

### DDR SDRAM: THE KEY SPECS

|          |                 |            | Clock Frequency  | Transfer 2 bits per clock | Data band        | width = 64-bit * transfer rate |

|----------|-----------------|------------|------------------|---------------------------|------------------|--------------------------------|

|          | Release<br>year | Chip       |                  | Bus                       |                  |                                |

| Standard |                 | Prefetch   | Clock rate (MHz) | Transfer rate (MT/s)      | Bandwidth (GB/s) | Voltage (V)                    |

| SDR      | 1993            | <b>1</b> n | 66 133           | 66 133                    | 0.53 1.06        | 3.3                            |

| DDR      | 1998            | 2n         | 100 200          | 200 400                   | 1.6 3.2          | 2.5                            |

| DDR2     | 2003            | 4n         | 200 533          | 400 1066                  | 3.2 8.5          | 1.8                            |

| DDR3     | 2007            | 8n         | 400 1066         | 800 2133                  | 6.4 17.066       | 1.5/1.35                       |

| DDR4     | 2014            | 8n         | 800 1600         | 1600 3200                 | 12.8 25.6        | 1.2/1.05                       |

| DDR5     | 2020            | 16n        | 1600 4400        | 3200 8800                 | 25.6 70.4        | 1.1                            |

| DDR6     | 2025            |            |                  | 12800 (17600)             | 102.4 (136)      |                                |

### **TYPICAL DDR TEST SCENARIOS**

#### I Focus on System Test:

- Measure signal integrity to verify quality of board design margin

- Prove signal integrity for customers

- Debug signal integrity issues on the memory interface

#### DDR SYSTEM – SIGNAL INTEGRITY LIMITS

#### **▶** Memory bus

- Source-synchronous bus with single-ended DQ and CA (X-talk, etc.)

- Multidrop bus with connects several DIMMs in parallel (trade density vs. speed)

- High load on CA bus (connects all DRAMs on a DIMM)

#### ► PCB board design

- Transmission lines

- Power supply

- Reference clock

- Isolation from other IPs

The transmission rate doubles from generation to generation.

The voltage level and margins reduce from generation to generation.

### (LP)DDR5 DETAILS

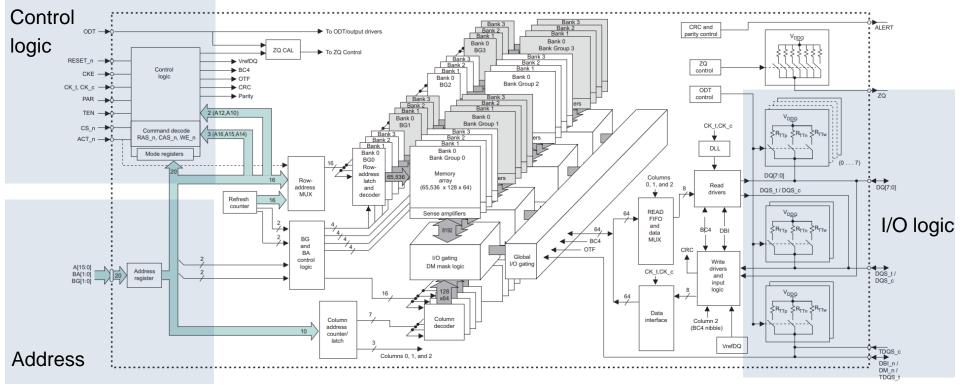

### **DDR SIGNALS FUNCTIONAL BLOCK DIAGRAM**

#### Source: JESD79-5C

### COMMAND TRUTH TABLE DDR5

- ► All SDRAM commands are defined by states of command bus

- ► Example DDR5:

- Signals are either command or address depending on ACT\_n

- Actived at the rising edge of the clock

- For Debugging Read / Write Separation

CS and CA4 are very useful

Table 30 — Command Truth Table

| Function                              | Abbrevia-<br>tion | CS n | CA Pins  |     |       |        |                |             |       |      |             |                |      | NOTES            |       |              |                      |            |     |      |      |      |            |           |

|---------------------------------------|-------------------|------|----------|-----|-------|--------|----------------|-------------|-------|------|-------------|----------------|------|------------------|-------|--------------|----------------------|------------|-----|------|------|------|------------|-----------|

|                                       |                   | L    | CA0      | CA1 | CA2   | CA3    | CA4            | CA5         | CA6   | CA7  | CA8         | CA9            | CA10 | CA11             | CA12  | CA13         |                      |            |     |      |      |      |            |           |

| Activate                              | ACT               | ΔCT  | ΔCT      | ACT | ACT   | ACT    | ACT            | L           | L     | L    | R0          | R1             | R2   | R3               | BA0   | BA1          | BG0                  | BG1        | BG2 | CIDO | CID1 | CID2 | 11, 17, 20 |           |

| , tour ato                            |                   | Н    | R4       | R5  | R6    | R7     | R8             | R9          | R10   | R11  | R12         | R13            | R14  | R15              | R16   | CID3/<br>R17 | ,, ==                |            |     |      |      |      |            |           |

| RFU                                   | RFU               | L    | Н        | L   | L     | L      | L              | V           | V     | V    | V           | ٧              | V    | V                | V     | V            |                      |            |     |      |      |      |            |           |

| 1410                                  |                   | Н    | V        | V   | V     | V      | V              | V           | V     | V    | V           | V              | V    | V                | V     | V            |                      |            |     |      |      |      |            |           |

| RFU                                   | RFU               | L    | Н        | L   | ш     | L      | Н              | V           | ٧     | V    | V           | ٧              | ٧    | V                | V     | V            |                      |            |     |      |      |      |            |           |

| 1410                                  | 1410              | Η    | V        | V   | ٧     | ٧      | ٧              | V           | V     | ٧    | V           | ٧              | V    | V                | V     | V            |                      |            |     |      |      |      |            |           |

| Write Pattern                         | WRP               | L    | Н        | L   | L     | Н      | L              | Н           | BA0   | BA1  | BG0         | BG1            | BG2  | CIDO             | CID1  | CID2         | 11, 15,<br>18,19, 20 |            |     |      |      |      |            |           |

| ···········                           | ••••              | Н    | V        | C3  | C4    | C5     | C6             | C7          | C8    | C9   | C10         | V              | Н    | н                | V     | CID3         | 18,19, 20            |            |     |      |      |      |            |           |

| Write Pattern w/                      | WRPA              | L    | Н        | L   | L     | н      | L              | Н           | BA0   | BA1  | BG0         | BG1            | BG2  | CIDO             | CID1  | CID2         | 11 15                |            |     |      |      |      |            |           |

| Auto Precharge                        |                   | Н    | V        | C3  | C4    | C5     | C6             | C7          | C8    | C9   | C10         | V or<br>DRFM=L | AP=L | н                | v     | CID3         | 11, 15,<br>18,19, 20 |            |     |      |      |      |            |           |

| RFU                                   | RFU               | L    | Н        | L   | L     | Н      | Н              | V           | V     | V    | ٧           | ٧              | ٧    | ٧                | V     | ٧            |                      |            |     |      |      |      |            |           |

| KFU                                   |                   | Н    | V        | V   | ٧     | V      | ٧              | V           | V     | V    | V           | V              | ٧    | V                | V     | V            |                      |            |     |      |      |      |            |           |

| Mode Register Write                   | MRW               | L    | Н        | L   | Н     | L      | L              | MRA0        | MRA1  | MRA2 | MRA3        | MRA4           | MRA5 | MRA6             | MRA7  | V            | 8, 11, 13,<br>20     |            |     |      |      |      |            |           |

| wode register write                   |                   | Ι    | OP0      | OP1 | OP2   | OP3    | OP4            | OP5         | OP6   | OP7  | V           | ٧              | CW   | V                | V     | V            | 20                   |            |     |      |      |      |            |           |

| Mode Register Read                    | MRR               | L    | Н        | L   | Н     | L      | Н              | MRA0        | MRA1  | MRA2 | MRA3        | MRA4           | MRA5 | MRA6             | MRA7  | V            | 8, 13, 21,           |            |     |      |      |      |            |           |

| meae riegieter rieau                  |                   | Н    | L        | L   | ٧     | V      | ٧              | V           | V     | V    | V           | V              | CW   | V                | V     | ٧            | 20                   |            |     |      |      |      |            |           |

| Write                                 | WR                | WR   | -        | Н   | L     | Н      | Н              | 4           | BL"=L | BA0  | BA1         | BG0            | BG1  | BG2              | CID0  | CID1         | CID2                 | 8, 12, 15, |     |      |      |      |            |           |

| · · · · · · · · · · · · · · · · · · · |                   | H    | <u> </u> | C3  | C4    | C5     | C <sub>6</sub> | <b>C7</b>   | C8    | C9   | C10         | ٧              | Н    | WR_<br>PartiaT=L | V     | CID3         | 19, 20               |            |     |      |      |      |            |           |

| Write w/Auto                          | WRA               |      |          | WD. | 14/04 | 14/5.4 |                | 14/04       | -     | Н    | L           | Н              | Н    | L.               | BL*=L | BA0          | BA1                  | BG0        | BG1 | BG2  | CID0 | CID1 | CID2       | 8, 12, 15 |

| Precharge                             |                   | Н    | V        | C3  | C4    | C5     | C <sub>6</sub> | C7          | C8    | C9   | C10         | V or<br>DRFM=L | AP=L | WR_<br>Partial=L | V     | CID3         | 19, 20               |            |     |      |      |      |            |           |

|                                       | RD                |      | Н        | L   | Н     | н      |                | BL =L       | BAO   | BA1  | BG0         | BG1            | BG2  | CIDO             | CID1  | CID2         | 8, 15, 19            |            |     |      |      |      |            |           |

| Read                                  |                   | Н    | C2       | C3  | C4    | C5     | C <sub>6</sub> | <b>-</b> 07 | C8    | C9   | C10         | ٧              | н    | ٧                | V     | CID3         | 20                   |            |     |      |      |      |            |           |

| Read w/Auto                           | RDA               | 7    | Н        | L   | Н     | Н      | Н              | BL*=L       | BA0   | BA1  | BG0         | BG1            | BG2  | CIDO             | CID1  | CID2         | 8, 15, 19            |            |     |      |      |      |            |           |

| Precharge                             |                   | H    | C2       | С3  | C4    | C5     | C <sub>6</sub> | C7          | C8    | С9   | C10         | V or<br>DRFM=L | AP=L | V                | V     | CID3         | 20                   |            |     |      |      |      |            |           |

| VrefCA Command                        | VrefCA            | L    | н        | н   | L     | L      | L              | OP0         | OP1   | OP2  | OP3         | OP4            | OP5  | OP6              | L     | V            |                      |            |     |      |      |      |            |           |

| VrefCS Command                        | VrefCS            | L    | н        | н   | L     | L      | L              | OP0         | OP1   | OP2  | OP3         | OP4            | OP5  | OP6              | н     | ٧            |                      |            |     |      |      |      |            |           |

| Refresh All                           | REFab             | L    | н        | н   | L     | L      | н              | CID3        | V     | v    | V or<br>RIR | V or H         | L    | CIDO             | CID1  | CID2         | 3, 23, 24            |            |     |      |      |      |            |           |

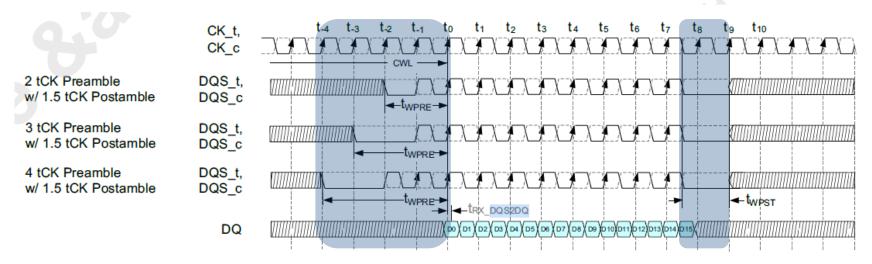

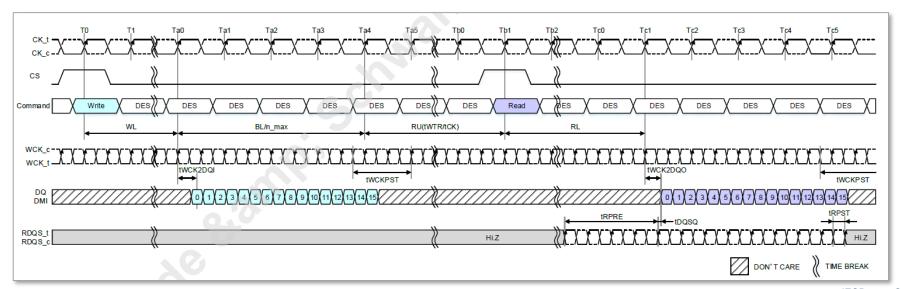

## PRE-/ POSTAMBLE TIMING VARIABLES - WRITE

#### ➤ Write:

Preamble: 2/ 3/ 4 tCK

Postamble: 0.5 or 1.5 tCK

DQS clock tree delay: tRX\_DQS2DQ

Table 146 — tRX DQS2DQ Offset Due to Temperature and Voltage Variation for DDR5-3200 to 4800

| Parameter                                 | Symbol              | DDR5-3200 |       | DDR5-3600 |       | DDR5-4000 |       | DDR5-4400 |       | DDR5-4800 |       | Unit        | Notes |

|-------------------------------------------|---------------------|-----------|-------|-----------|-------|-----------|-------|-----------|-------|-----------|-------|-------------|-------|

| Farameter                                 |                     | Min       | Max   | Unit        | Notes |

| DQS to DQ offset<br>temperature variation | tRX_DQS2DQ<br>_temp | -         | 12.75 | -         | 11.34 | -         | 10.20 | -         | 9.28  | -         | 8.50  | ps/10°C     | 1,3   |

| DQS to DQ offset<br>voltage variation     | tRX_DQS2DQ<br>_volt | -         | 45.00 | -         | 43.00 | -         | 41.00 | -         | 39.00 | -         | 32.00 | ps/<br>50mV | 2,3   |

NOTE 1 tRX\_DQS2DQ max delay variation as a function of temperature

NOTE 2 tRX\_DQS2DQ max delay variation as a function of the DC voltage variation for VDDQ and VDD. It includes the VDDQ and VDD AC noise impact for frequencies >20MHz and max voltage of 45mVpA-pk from DC -20MHz at a fixed temperature on the package. For tester measurement VDDQ=VDD is assumed.

NOTE 3 Absolute value of DQS to DQ offset

## DDR5-4800 SINGLE RANK UDIMM (CRUCIAL) WRITE

Rohde & Schwarz

#### LPDDR5 SIGNALS

- ► New: Two forwarding Strobe Clock signals:

- WCK: timing reference for WRITE data capture and READ data output

- RDQS: is derived from WCK and timing reference for READ

#### (LP)DDR5 Details

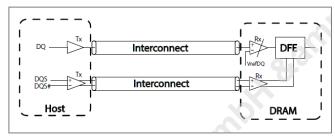

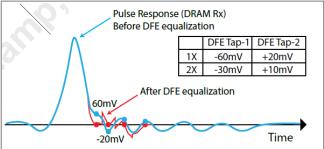

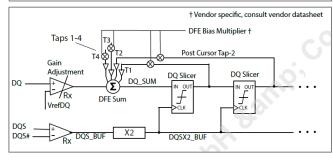

#### **DFE**

- ► ISI due to reflections is particular concern for DDR5

- ▶ 4-tap DFE for data rates >= 2933 MT/s

- Gain amplifier

- DFE summer

- 4 DQ slicers (tabs) looping back to summer

- ► Mode Register to define DFE settings for memory controller

- Optimal settings are system dependent

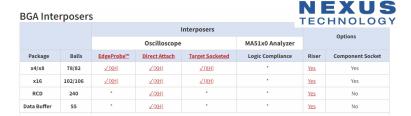

### CONTACTING THE DDR INTERFACE VIAS, INTERPOSERS

- DDR JEDEC compliance focus on SDRAM chip and specifies measurement at package ball

- On single-sided DIMM or PCB, it is still possible to probe behind the package

- For design without access to back of PCB, interposer is required

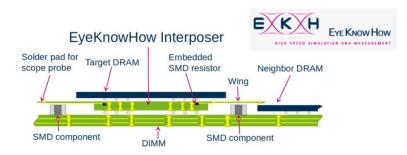

- For interposers we refer to Nexus or EyeKnowHow

Rohde & Schwarz

Interposer solution from EKH

## (LP)DDR5 SIGNAL INTEGRITY DEBUGGING THE POWER OF THE ZONE TRIGGER

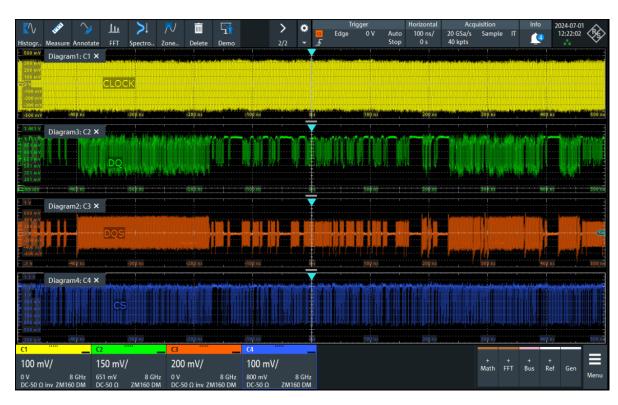

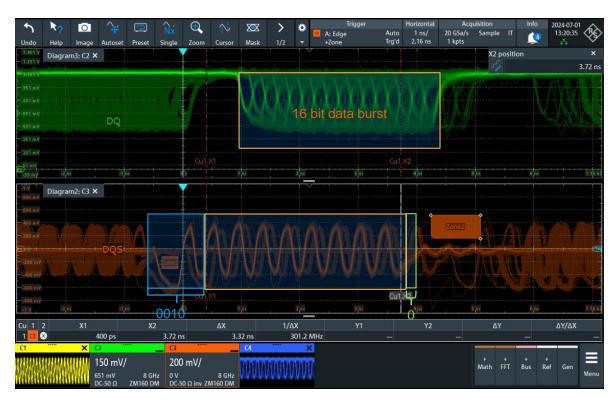

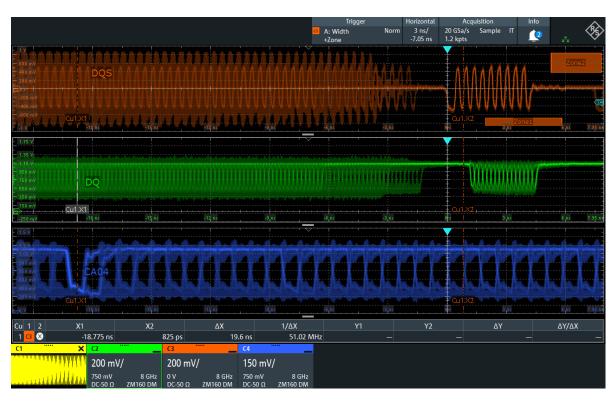

## THE POWER OF ZONE TRIGGER SIGNAL OVERVIEW

- ► Single Acquisition over a longer time scale (e.g. 1us)

- ▶ In the example an amplitude difference for different bursts at DQ and DQS is visble

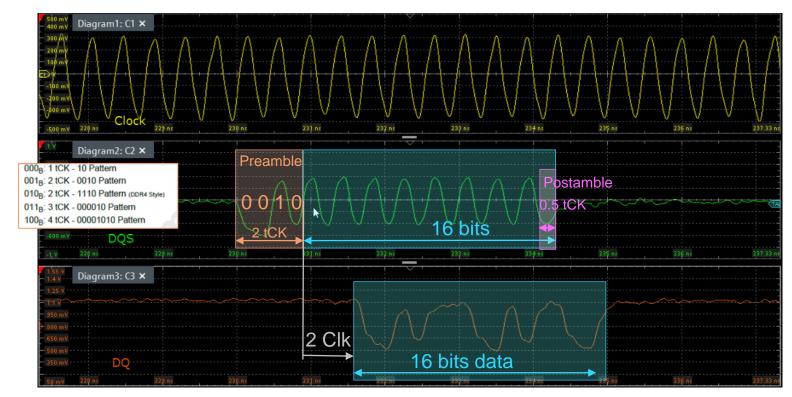

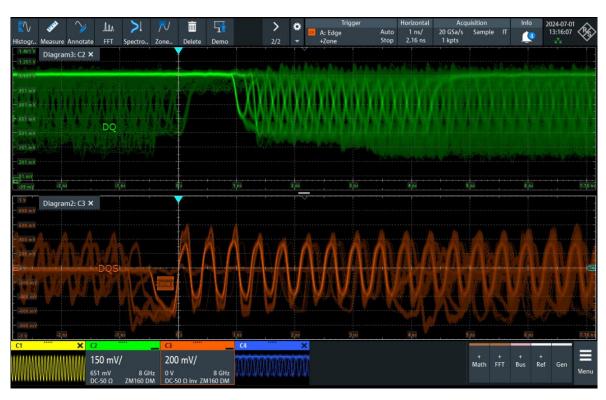

## THE POWER OF ZONE TRIGGER PRE-/ POSTAMBLE

- ► The pre- and postamble depends on the data rate and system configuration.

- With the Zone trigger you easily can focus the acquisition on Read or Write bursts

- ► Focus on short bursts

## THE POWER OF ZONE TRIGGER PRE-/ POSTAMBLE: WRITE

- **▶** Preamble:

- Pattern 0010 2 tCK

- **▶** Postamble:

- Pattern 0 0.5tCK

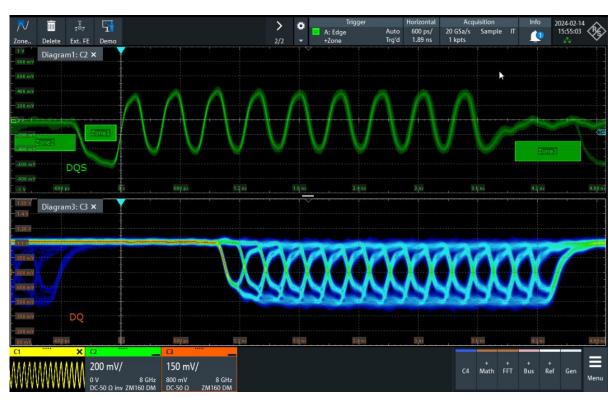

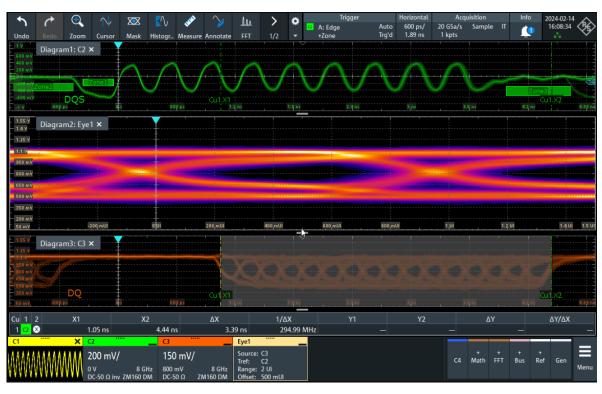

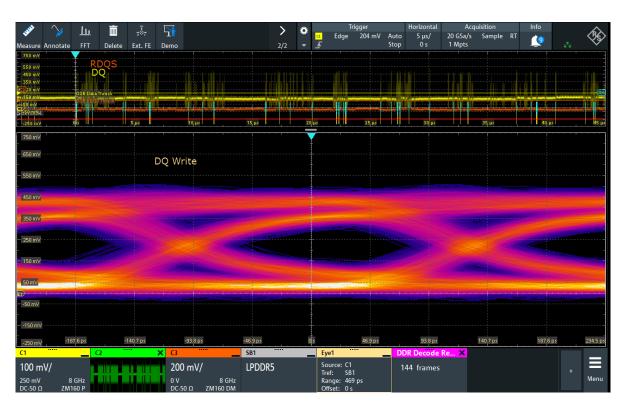

### THE POWER OF ZONE TRIGGER ISOLATING WRITES FOR DATA EYES

▶ Use Zone Trigger for Read/ Write burst separation and respective eye analysis

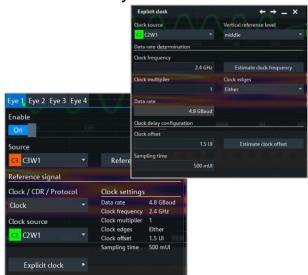

### THE POWER OF ZONE TRIGGER **EYE DIAGRAM - WRITE BURSTS**

- ▶ Gate focusing on the WRITE bursts

- ► Explicit clock with respective clock delay

Rohde & Schwarz

### THE POWER OF ZONE TRIGGER VERIFY CL/CWL LATENCY

- ▶ Use Zone Trigger for R/W burst separation and respective eye analysis

- ► Apply "Persistence Mode"

- Measure Latency on CS and CA04

## (LP)DDR5 SIGNAL INTEGRITY DEBUGGING DDR PROTOCOL DECODE (READ/ WRITE)

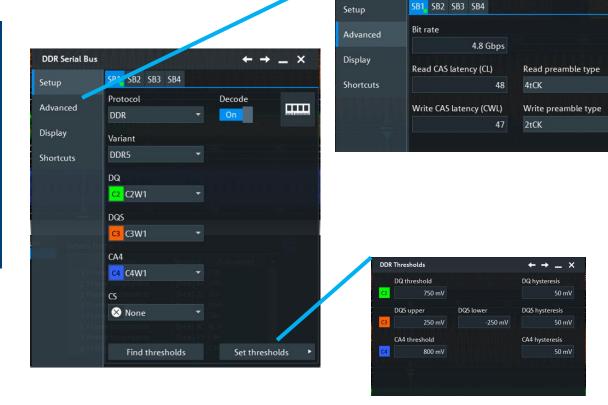

#### PROTOCOL DECODE: READ/WRITE

- ▶ DDR5 Decode:

- based on CL/CWL and Preamble

- DQ, DQS, CA04

- ► LPDDR5 Decode:

- Based on RDQS toggling

- DQ, WCK, RDQS

**DDR Serial Bus**

## PROTOCOL DECODE: READ/WRITE DDR5-4800

► Read/ Write Decoding Example at 4800 Mbit/s

Rohde & Schwarz

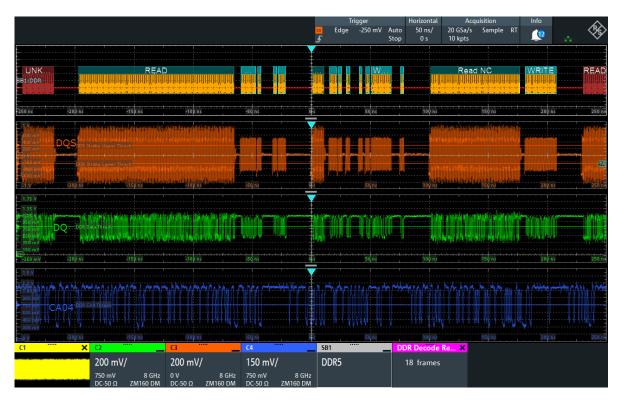

## PROTOCOL DECODE: READ/WRITE DDR5-4800

▶ Decode table

## PROTOCOL DECODE: READ/WRITE DDR5-4800

Scaling in to Result details

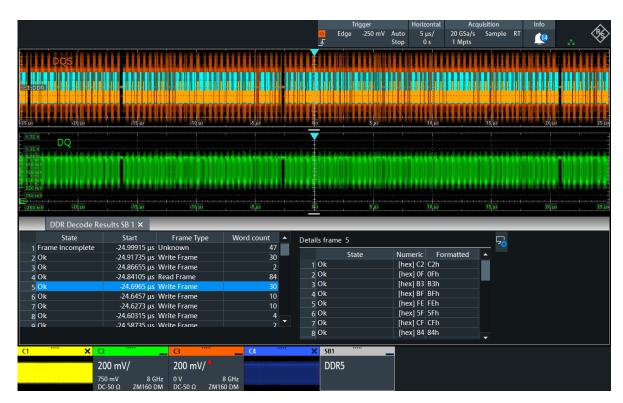

## PROTOCOL DECODE: READ/WRITE LPDDR5-4267

Scaling in to Result details

Rohde & Schwarz

## (LP)DR5 SIGNAL INTEGRITY DEBUGGING DDR EYE

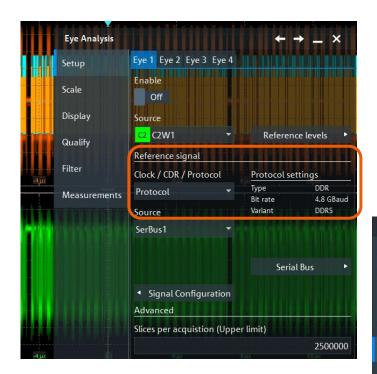

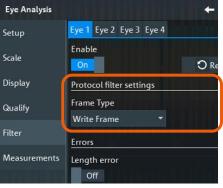

## DATA EYE ANALYSIS BASED ON DDR PROTOCOL DECODE

#### ► DDR Data Eye:

- DDR protocol as timing reference

- Use the power of the Advanced Eye function

- Filter to distinguish Read and Write Eyes

Rohde & Schwarz

### **DATA EYE ANALYSIS BASED ON DDR PROTOCOL DECODE: DDR5-4800**

► READ & WRITE DQ data eyes

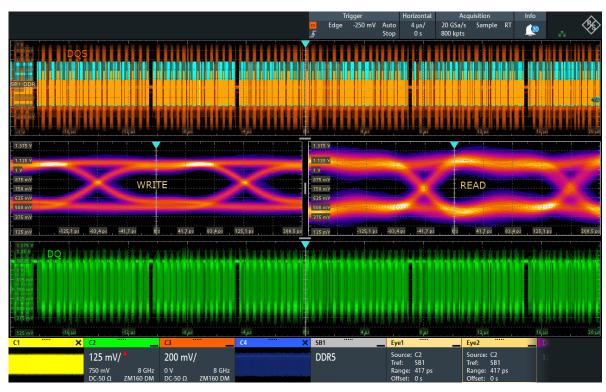

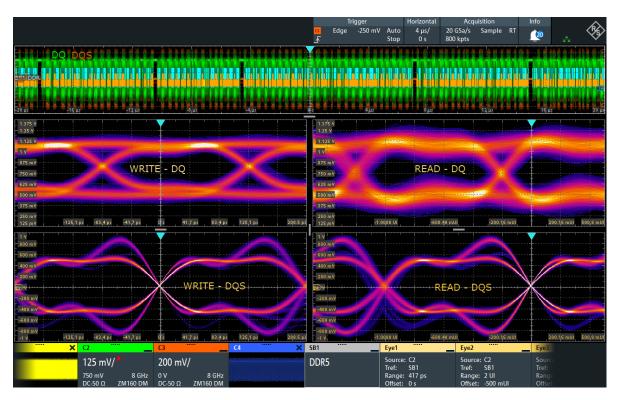

## DATA EYE ANALYSIS BASED ON DDR PROTOCOL DECODE: DDR5-4800

READ & WRITE DQ data and DQS strobe clock eyes

Rohde & Schwarz

## DATA EYE ANALYSIS BASED ON DDR PROTOCOL DECODE: LPDDR5-4267

► WRITE DQ data

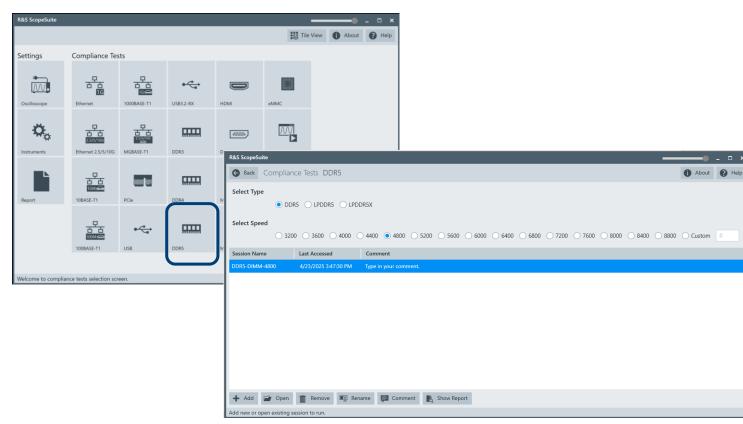

### **COMPLIANCE TESTING**

#### DDR5 - SCOPESUITE

- ▶ DDR5 Tile

- **▶** Select Type

- DDR5

- LPDDR5

- LPDDR5X

- ► Select Speed:

- JEDEC speed grade or

- Custom

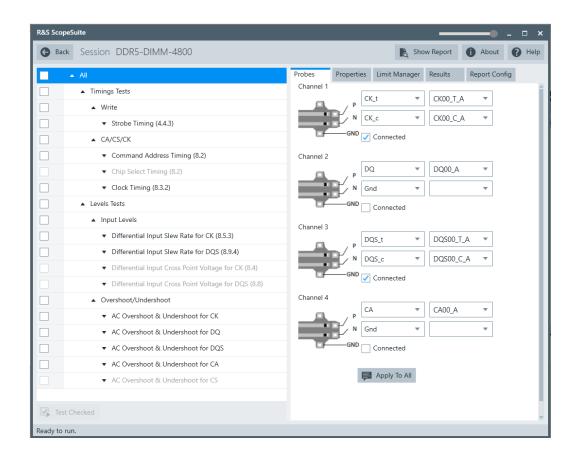

## DDR5 – SCOPESUITE PROBE SETUP

- ► New flexibility for Signal-to-Probe configuration:

- use single-ended mode to connect to two DQ or CA signals

use diff mode for connecting to se signals

- ► Probe labels for

- CLK, DQ, DQS, CS and CA signals

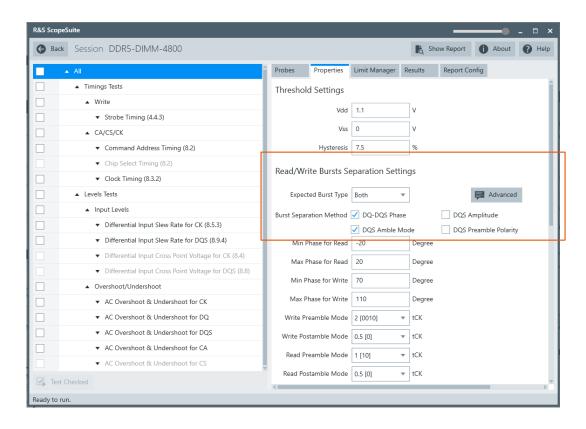

## DDR5 – SCOPESUITE PROPERTIES

- ► Flexible Read / Write separation

- DQ-DQS Phase

- DQS Amplitude

- DQS Preamble Pattern

- DQS Preamble Polarity

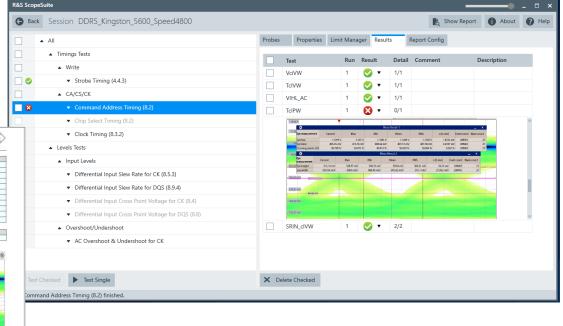

## DDR5 – SCOPESUITE RESULTS DDR5-4800

► Results per test item within the ScopeSuite application

▶ Detailed Report

VolVW: CA

DDR5 Memory Interface - Signal Integrity Debugging & Compliance Testing **DEMO**

### **SUMMARY**

### **SUMMARY**

- ► The need for memory continuously increases

- Data rates are increasing, voltage levels decreasing

- ► RTP's 16 GHz covers DDR5

- ► The RTP can address SI debugging with Zone Trigger and Advanced Eye

- R&S addresses compliance testing with dedicated options for DDR5 and LPDDR5

#### Find out more

### www.rohde-schwarz.com/rtp

#### ROHDE&SCHWARZ

Make ideas real